2. 国家超级计算郑州中心, 郑州 450001

2. National Supercomputing Center in Zhengzhou, Zhengzhou 450001, China

芯片是现代科技发展的关键, 应用范围广, 市场需求更替速度快. System on chip (SoC)芯片设计越来越复杂, 工艺要求越来越高, 做好一颗芯片的难度越来越大, 芯片验证作为现代大规模芯片开发周期中最关键环节之一, 其技术发展也在快速更迭, 验证方法学(universal verification methodology, UVM)[1]汲取继承了OVM和VMM的优点, 是当前主流的验证方法学[2], 极大提高了验证工作效率[3]. SATA (serial advanced technology attachment)串行高级技术附件[4]协议是由 Mentor、Cadence 等公司组成的Serial ATA 委员会提出的一种串行硬件接口规范, 主要用于主板和存储设备之间传输数据. SATA装置简单、容量高、易使用, 经济价格实惠, 广泛应用于固态硬盘、存储器、服务器等. 自研高性能安全存储SoC芯片中集成设计了SATA Host与SATA Device模块, 在系统层面上为验证确保 SATA Host和 Device之间的数据通路是符合设计预期, 能够正常运行, 本文在基于UVM验证方法学的系统级验证平台上对SATA Host[1]与Device之间的数据通路进行验证, 通过对自研 高性能安全存储SoC芯片的架构分析及SATA协议理解, 确定系统级SATA数据通路的验证方案, 设计测试用例进行仿真验证. 结合对仿真结果波形的分析, 验证了预期设计目标.

1 安全存储芯片架构及SATA协议数据传输简介 1.1 高性能安全存储SoC芯片简介高性能安全存储SoC芯片[5]是一款面向多种存储介质数据安全传输和访问控制需求, 具有高集成度、高兼容性、高安全可靠性等特点的新一代国产自主可控存储安全SoC芯片. 高性能安全存储SoC芯片以ASIC设计思想为核心[6], 采用具有自主知识产权的国产龙芯LS232嵌入式CPU, 采用成熟的32位多层AMBA[7]总线矩阵技术作为互联枢纽. 除实现时钟、复位、中断及系统控制等基本功能, 该款芯片达到国密二级安全标准, 支持硬件逻辑电路实现身份认证与数据流加解密相结合的双重安全机制, 支持SM1/2/3/4/9系列商用密码算法的硬件电路实现, 保留算法可编程、可重组的基础硬件资源, 保留与外部高等级密码算法芯片连接的数据接口, 轻松实现升级密码算法等级. 外设接口方面该SoC芯片集成设计实现PCIE、USB、网络QOS及主从SATA II/III等高速接口, 支持高速native command queuing (NCQ)队列操作; 此外该芯片具备丰富的UART、SPIM、SPIS、IIC等低速接口, 支持实现电压、频率、温度及光检测等功能. 芯片自主完成全部功能, 不依赖于操作系统或其他上位机软件, 具体安全存储SoC芯片架构如图1所示.

|

图 1 高性能安全存储SoC芯片架构 |

1.2 SATA协议数据传输简介 1.2.1 SATA协议层简介

SATA协议[4]采用点对点拓扑结构进行数据传输通信, 协议借鉴TCP/IP模型, 由应用层、传输层、链路层及物理层4层构成, 如图2所示. 应用层与主机进行交互, 负责整个ATA命令执行. 传输层对在主机和设备之间传输的控制信息和数据进行FIS帧封装与解封装. 链路层包含十几种原语, 包括用于标志帧起始和结束的SOF和EOF原语, 用于防止数据传输溢出控制的HOLD原语等. 链路层通过这些原语实现对数据流传输及帧的控制, 并使用8b/10b对每个字节进行编码或解码, 插入控制字符, 以便正确解码10位数据流. SATA协议的物理层实现数据流的串并转换, 以串行数据流的形式发送和接收编码后的数据信息[4]. 在SATA协议数据通路建立链接的初始阶段将通过链路层或物理层产生COMMREST、COMMIT、COMWAKE等OOB原语进行链接建立的握手响应.

|

图 2 SATA协议结构 |

1.2.2 SATA协议数据传输过程简介

SATA协议通过执行direct memory access (DMA)、programmed input/output (PIO)、NCQ[4]等读写命令的方式实现对数据传输控制, 不同命令的实际读写操作过程基本相似. 以典型的Host对Device的DMA方式读写数据操作为例, 图3和图4分别展示了DMA命令方式数据读和写的操作过程. DMA命令读方式中, Host和Device都初始化准备完成后, 软件对Host DMA控制器进行初始化配置, 向Device发送读命令Register H2D FIS帧, 设备分析执行命令并且准备data FIS发送给主机, 主机接收data FIS将数据存入内存, Device发送完本次请求数据后, 给主机发送Register D2H帧, 告知本次命令数据传输请求结束. DMA写命令操作过程与读操作类似, 软件对Host DMA控制器进行初始化配置, 向Device发送写命令Register H2D FIS帧, 设备分析执行命令, 向Host发送DMA Activate FIS告知Host准备好接收数据, Host通过data FIS给Device发送准备好的数据, Device接收数据并存入内存, Device完成本次数据传输接收后, Device给Host发送Register D2H FIS帧, 告知本次命令数据传输请求结束. 对于多次数据传输, Device在接收每一次data FIS前都要向Host发送DMA Activate FIS告知Host准备好接收数据.

|

图 3 DMA读命令过程 |

|

图 4 DMA写命令过程 |

2 高性能安全存储SoC芯片系统SATA通路验证实现

高性能安全存储SoC芯片[5]集成了兼容SATA 3.0及以下各版本协议的SATA Device IP和Host IP, Host IP通过PHY模块[8]实现与外部支持SATA协议的存储介质链接进行数据传输; Device IP通过PHY模块与支持AHCI/SCSI兼容SATA协议的主机进行互联传输数据. 在SoC芯片系统层面设计中, SATA Host和Device构成一个数据传输通路, 该通路上可以传输两种数据流, 一种是经过加解密功能模块处理后的数据流, 一种是直通数据流模式. 直通数据流模式是进行加解密数据流模式的前提, 因此本文以直通数据流方式作为验证对象进行系统数据通路验证, 为后续进行加解密通道验证奠定基础. 为了进行可控配置SATA IP和Device IP的缓存数据深度及缓存加解密模式下待处理数据[9], 设计中使用自主设计优化的外部FIFO替代IP模块自带的FIFO, 具体拟验证SATA直通数据流通路如图5所示, 其中PC机使用SATA HOST VIP替代, Device model模拟存储介质的行为, 实现Device读写操作的响应.

|

图 5 直通数据流通路 |

2.1 验证环境

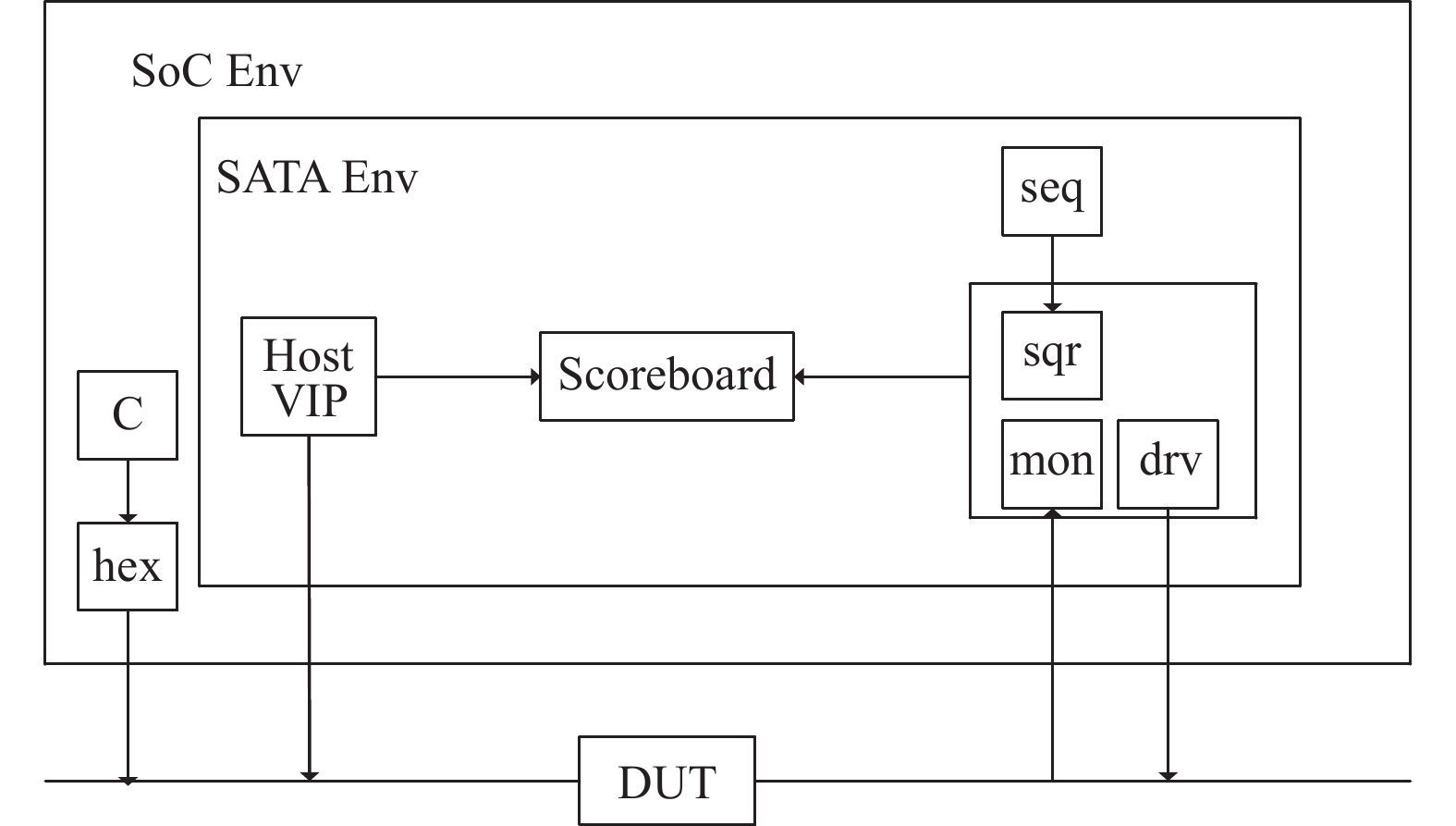

图6为利用SATA Host VIP及基于UVM[10]验证方法学构建的系统层面SATA通路验证平台示意图. SATA Host VIP实现SATA Host端相关命令协议, 依据配置的命令工作方式发送/接收相关控制或数据帧; device agent[11]实现对SATA存储介质读写过程的响应操作模拟, SATA Scoreboard[12]对接收到来自Host VIP和Device agent[13]的数据进行对比判断. 在验证的过程中, 通过对SATA协议具体命令方式数据传输过程的理解, 设计系统层面测试用例[14], 编写相关C固件程序, 通过交叉编译生成hex文件加载到SoC芯片系统中仿真运行.

|

图 6 SATA通路验证平台示意图 |

2.2 SATA通路验证测试用例设计 2.2.1 用例测试点说明

本文在系统层面对SATA 通路的直通数据流模式进行验证, 主要关注SATA Host与SATA Device在系统中以不同命令方式进行数据交互传输的通路测试, 包括DMA、PIO、NCQ数据传输功能、NDC非数据命令测试[15], 除了对SATA通路进行数据传输功能测试, 还进行了数据异常处理测试来确保验证的完备性. 依据SATA协议和实际芯片功能需求, 提取测试功能点并编写了表1中所列基于C语言的测试用例表, 数据传输测试功能点与测试用例一一对应. 以典型的DMA数据传输方式为例进行详细用例描述.

① 寄存器读写功能测试

读出SATA寄存器的初始值, 对SATA的全局和端口寄存器全写1, 读出寄存器数据与spec规定的初始值进行对比, 通过分析寄存器的读写情况对前端设计进行初步的判断.

② 低功耗模式测试

为接收的fis配置内存空间, 配置PCMDR寄存器, 将SATA带入partial低功耗状态, 检测链路的状态, 配置PCMDR寄存器使得SATA进入active状态, 轮询检测链路的状态.

| 表 1 测试用例列表 |

③ DMA数据传输测试

建立SATA Device所用接收和发送FIS结构体, 分配接收FIS的地址. 循环检查寄存器PSSTSR, 直到interface在active态, 速度为非0, Host检测存在. Device接收FIS并且分析FIS的command确定是读命令还是写命令, 如果是DMA写命令, 则配置prd链表进行接收, 配置接收数据长度、几个prd等, 配置PCMDR的ST位和PDTR位中相应的命令槽, 开始接受数据, 轮询检测是否接收完成. 接收完成后, 配置寄存器PCMDR, 发送寄存器帧, 检查寄存器PCMDR的TXREG位, 如果为0则表示写操作完成. DMA读命令的测试过程与写命令测试过程类似, 只不过读命令与写命令的数据方向相反, 最后只需检测PCMDR寄存器的TXREG位, 为0则说明读操作完成.

④ 数据异常处理测试

数据异常处理测试是对待测设计注入错误测试用例, 即SATA通路在碰到错误帧时, 是否能够继续保持正确, 从而避免发送错的数据. 使用一个错误的FIS替换正确的FIS, 查看SATA的端口中断寄存器是否能将相关位进行置位, 并利用测试用例轮询检查错误状态位置.

2.2.2 用例关键数据结构定义设计的验证C固件程序测试用例在参与到具体数据传输中需要支持对部分SATA协议命令功能进行交互, 在启动任何数据传输操作之前, 固件必须构造数据传输中必须的物理区域描述符表、命令列表和FIS内存结构, 在测试用例中则通过定义数据结构体实现. 用例中部分关键数据结构体定义如下.

物理区域描述符表结构体定义:

typedef struct prd_entry

{

u32 dba; /*Data base Address*/

u32 dba_up; /*Data base Address Upper 32-bits*/

u32 rev;

u32 dbc_i;

}tx_prd_entry;

命令表的命令头结构体定义:

typedef struct cmd_hdr_entry_d

{

u32 prdtl_attr; /*Physicial region length*/

u32 dmatc; /*DMA Transfer Count*/

u32 dmabo; /*DMA Buffer offfset*/

u32 prdtba; /*prd table base address*/

u32 prdtbau; /*prd table base address upper 32 bits*/

u32 rev[3];

}tx_cmd_hdr_entry_d;

FIS内存结构体定义:

typedef fis_share_area

{

u32 h2d_fis[5];

u32 d2h_fis[5];

u32 pio_fis[5];

u32 sdb_fis[7];

}tx_fis_share_area;

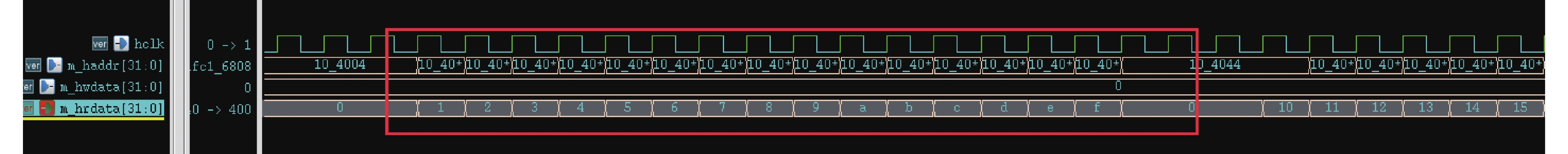

3 仿真结果分析

|

图 7 链路建立OOB上电序列 |

|

图 8 数据传输中系统memory中缓存的数据 |

|

图 9 错误状态位置 |

4 结束语

本文主要对高性能安全存储SoC芯片中SATA直通数据通路进行验证, 在充分对芯片架构理解的基础上设计确认系统层面的验证通路结构, 结合对SATA协议的理解设计相关命令方式数据传输测试用例[2]. 通过对结果的分析证明系统集成设计中实现了预期的通路功能, 系统层面上SoC芯片是能够调度协调多个子模块正常工作的. 同时, 也对后期进行加解密数据通路验证铺垫了基础.

| [1] |

徐佳安. 基于UVM的SATA AHCI验证[硕士学位论文]. 上海: 上海交通大学, 2019.

|

| [2] |

刘斌. 芯片验证漫游指南: 从系统理论到UVM的验证全视界. 北京: 电子工业出版社, 2018.

|

| [3] |

Raghuvanshi S, Singh V. Review on universal verification methodology (UVM) concepts for functional verification. International Journal of Electrical, 2014, 2(3): 101-107. |

| [4] |

SATA-IO. Serial ATA advanced host controller interface (AHCI) spec revision 3.4. SATA-IO, 2018.

|

| [5] |

于哲. 新一代移动安全存储控制SoC芯片设计[硕士学位论文]. 天津: 天津大学, 2013.

|

| [6] |

刘达, 倪伟, 徐春琳. 基于UVM的AXI总线验证IP设计. 微电子学, 2019, 49(5): 680-685. DOI:10.13911/j.cnki.1004-3365.180463 |

| [7] |

王兴耀, 戴宇杰. 基于UVM的AHB-UART模块验证. 南开大学学报(自然科学版), 2020, 53(5): 82-86. |

| [8] |

程晓航. 基于FPGA的SATA盘大容量存储系统的设计与实现[硕士学位论文]. 西安: 西安电子科技大学, 2019.

|

| [9] |

王晶, 赵云鹏, 池骋. 一种SATA固态硬盘Power Cycle功能自动化测试方法. 微电子学与计算机, 2021, 38(8): 40-44. |

| [10] |

刘森态, 庞宇, 魏东. 基于UVM的Wishbone-SPI验证平台设计. 电子技术应用, 2022, 48(6): 36-41. |

| [11] |

徐梓文, 郭桂良. 基于功能覆盖率的MAC的UVM验证. 计算机与数字工程, 2021, 49(11): 2282-2286. DOI:10.3969/j.issn.1672-9722.2021.11.021 |

| [12] |

Wang J, Wang F. An advanced verification platform based on UVM. Applied Mechanics and Materials, 2014, 670–671: 1441–1446.

|

| [13] |

田晓旭, 徐庆阳, 汤先拓, 等. 基于UVM的寄存器验证自动化方法. 集成电路应用, 2020, 37(2): 18-21. |

| [14] |

Kamireddy LS, Kamireddy LS. UVM based reusable verification IP for wishbone compliant SPI master core. International Journal of VLSI Design & Communication Systems, 2018, 9(5): 21-29. |

| [15] |

张宇. 固态硬盘中SATA接口控制器命令层的设计及验证[硕士学位论文]. 南京: 南京理工大学, 2014.

|

| [16] |

Yang Z, Xu H, Li N, et al. FPGA logic design of SATA3.0 physical layer. Proceedings of the 2015 IEEE 11th International Conference on ASIC. Chengdu: IEEE, 2015. 1–4.

|

2023, Vol. 32

2023, Vol. 32