2. 浪潮电子信息产业股份有限公司, 济南 250013

2. Inspur Electronic Information Industry Co. Ltd., Jinan 250013, China

指令集, 是在CPU设计初期规定, 用于控制处理器内部运行的一系列指令的集合. 指令集设计的优劣, 对CPU的性能有重要影响. RISC-V指令集[1]是2014年发布的一套完全开源的精简指令集(RISC), 始于加州大学伯克利分校的相关项目. 凭借前瞻性的设计与后发优势, RISC-V成为了开放指令集架构领域的佼佼者.

图灵奖得主John Hennessy曾经就未来的芯片设计提出了一种DSA (Domain Specific Architecture)的概念, 即针对应用领域做优化的处理器架构. ARM作为一种通用且固化的指令集架构, 设计灵活性有限, 而RISC-V架构不仅仅开源, 同时还具有模块化、可扩展的特点, 支持用户自定义指令.

服务器管理控制器是应用于服务器等数据中心基础设施的一种专用SoC, 主要功能包括对系统设备进行信息监测、记录以及恢复等, 它以独立系统运行, 通过网络还可以实现对服务器的远程访问、远程监控和管理[2]. 目前, 服务器管理控制器主要基于ARM架构处理器进行设计, 尚未有公开的基于RISC-V设计方案. 本文从SoC设计底层入手, 基于RISC-V架构处理器进行服务器管理控制器的设计和测试, 探究方案可行性并与ARM架构进行对比.

本文首先介绍了RISC-V及开源乱序执行处理器BOOM[3,4], 然后详细描述了基于该处理器实现服务器管理控制器FPGA原型系统的过程. 该原型系统移植了OpenBMC开源组件, 实现了智能平台管理接口规范(Intelligent Platform Management Interface, IPMI)协议的基本功能, 同时还介绍了LXDE等定制化组件. 本文主要工作是验证了RISC-V替代ARM设计服务器管理控制器的可行性和性能水平.

1 RISC-V与BOOM介绍自RISC-V发布以来, RISC-V的工具链与产品越发多样, 生态逐步完善. 2015年, 非盈利组织RISC-V基金会(RISC-V Foundation)成立, 着手构建开放、合作的软硬件交流平台, 推动RISC-V生态的快速完善与发展. 很快就有几百家加入了基金会, 其中包括谷歌、IBM、英伟达、浪潮等国际企业以及加州大学伯克利分校、麻省理工学院、普林斯顿大学、中科院计算所等学术机构.

在国内, 芯来科技于2017年10月开源了其“蜂鸟”低功耗处理器, 这是国内由企业开源的第一款基于RISC-V架构的处理器. 目前在中国已经有多家成熟的RISC-V CPU企业, 如睿思芯科、平头哥等. 在物联网、智能家电等领域, RISC-V相关产品已经有大量应用案例. 目前, 基于RISC-V架构的开源处理器已经涵盖嵌入式、AI、5G射频、硬盘控制器等多种应用场景. 处理器核心也由最初的低功耗标量处理器逐渐向乱序超标量的复杂架构演进[5]. 产业环节中的各种相关工具如GCC/LLVM编译器、Linux内核支持、高层次设计语言、总线通讯协议等也在不断完善.

在2015年, 伯克利分校的研究团队推出了基于RISC-V架构的乱序执行核心BOOM (Berkeley Out-of-Order Machine), 并将其完全开源. 这款CPU使用Chisel语言编写, 指令集为RISC-V中的RV64G指令和特权指令, 该核心是一款64位RISC-V超标量Berkeley乱序机的源存储库, 计算性能与ARM中高端处理器相当, 经过多次流片, 实际性能表现优异.

BOOM的流水线结构主要分为6个阶段: 取指、译码/重命名/指令调度、发射/读寄存器、执行、访存以及写回. 由于Chisel是一种面向硬件的高层次设计语言, BOOM处理器可以实现参数的灵活配置, 包括: 取指宽度、译码宽度、指令发射宽度、物理寄存器堆的大小、有序发射或无序发射; L1 Cache及L2 Cache的路数等参数. BOOM流水线结构[3]如图1所示.

|

图 1 BOOM处理器流水线结构 |

2 控制器原型设计

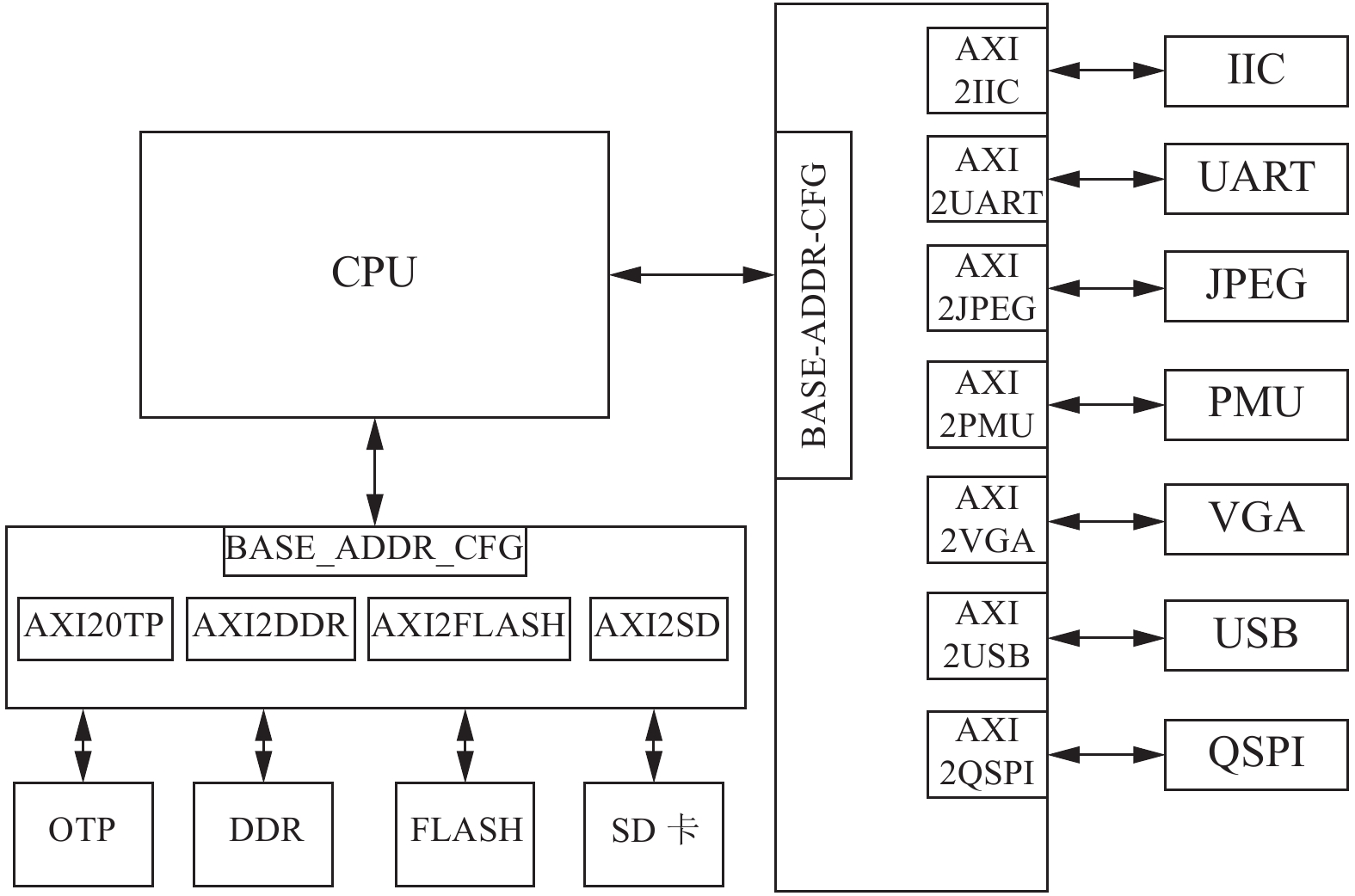

常见的服务器管理控制器的基本架构如图2所示. 本文依托RISC-V开源生态环境, 设计实现了管理控制器基本的外设和接口模块, 包括:

1) I2C/SMBus: 用于实现与CPLD的通信和获取温度、电压等传感器回传的数据;

2) LPC: BIOS与监控管理系统之间通信, BIOS向监控管理系统上报启动信息;

3) KVM: 视频、鼠标和键盘的控制信息重定向到监控管理系统;

4) SPI: BIOS固件的升级更新接口;

5) JTAG: CPLD的固件更新接口;

6) IPMB: ME (Management Engine)与监控管理系统之间的通信;

7) Ethernet: 监控管理系统接入网络接口;

8) VGA: 实现视频流的显示;

9) PWM: 实现风扇转速的控制和监控;

10) USB: 鼠标、键盘等USB设备接口;

11) Timer、RTC、WDT等基础模块: 实现复位、实时时钟等.

|

图 2 通用RISC-V 原型系统架构 |

RISC-V控制器FPGA原型平台处理器选型工作中, 我们对比了开源的Rocket[6]、BOOM、PULPino[7]等, 通过公开的性能数据分析, 选用性能最优, 并经流片验证的BOOM V2核心, 并基于BOOM V2 SoC开发环境进行开发. 将上述外设、接口模块与处理器核心进行集成后, 对系统地址空间进行了划分, 同时, 利用RISC-V的工具链对OpenBMC系统进行重新编译和文件系统移植.

本文主要从4个方面对FPGA原型平台进行了功能扩展和优化:

1) 原型系统主处理器实现了BOOM双核, 嵌入L2 Cache和一致性协议总线, 实现核间Cache一致性. 实际应用可以对核数配置, 满足不同场景性能需求.

2) 针对BOOM总线进行了扩展优化, 增加对AXI总线的扩展支持, 并基于该总线扩展了DDR等外设接口.

3) 鉴于RISC-V指令集的灵活性, 对指令集进行了向量指令扩展[8]的探索. RVGC64指令集目前已经满足SoC设计需求, 扩展的向量指令主要目的是探究RISC-V扩展指令集开发流程, 为其他高性能应用场景提供支持.

4) DRAM容量达到8 GB, 系统启动时, 通过DDR将固件直接加载到DRAM中, 加快固件加载和系统启动速度.

2.1 基于RISC-V的控制器系统结构服务器管理控制器主要利用传感器监控计算机或服务器的运行状态[9], 具有本地和远程诊断、控制台支持, 配置管理, 硬件管理和故障排除等功能.

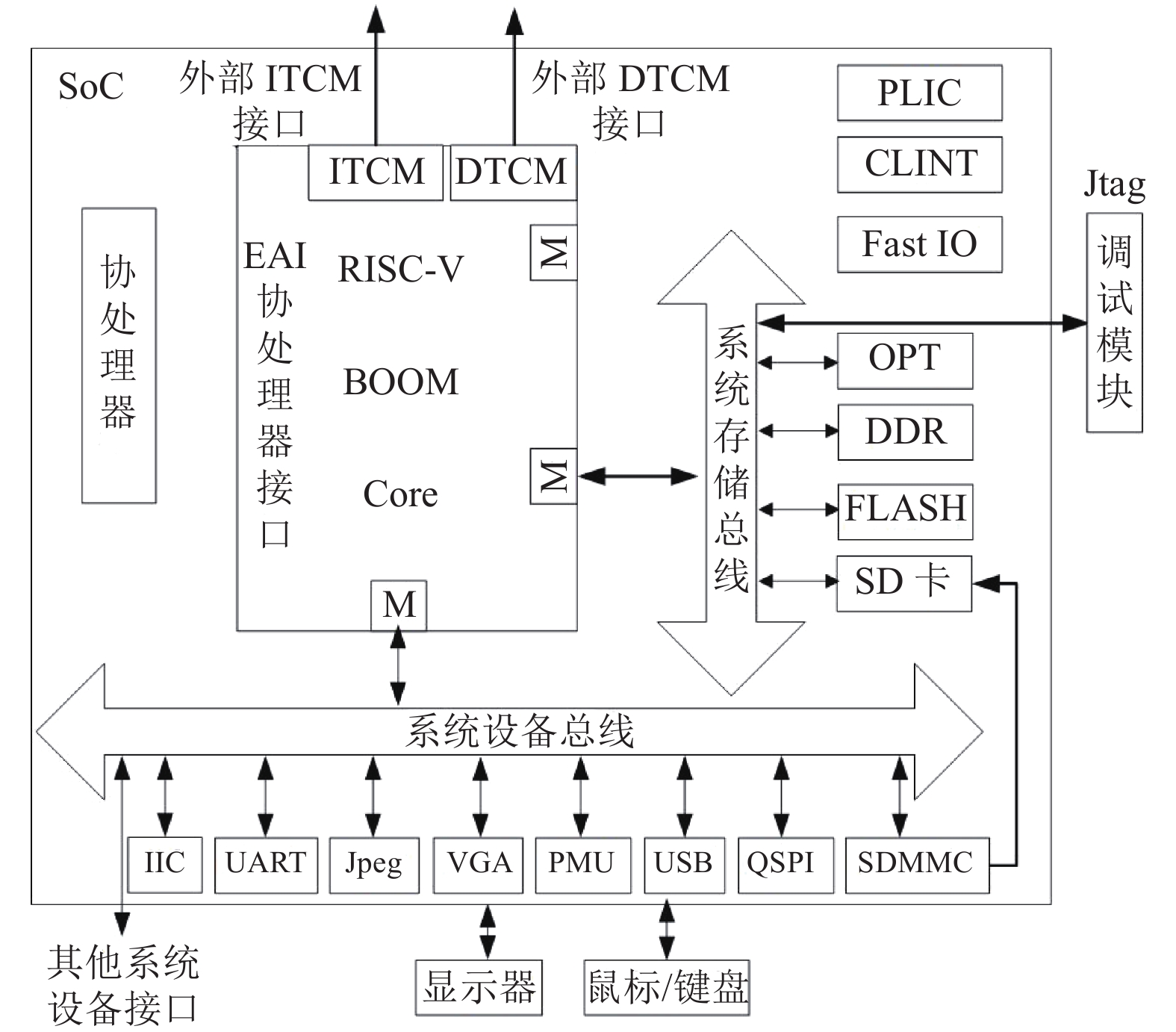

我们结合服务器管理控制器实际应用场景, 进行了RISC-V SoC的定向设计与优化, 控制器结构如图3所示. SoC采用双核BOOM作为主处理器, 集成服务器管理控制器所需IIC、LPC、QSPI等外设接口, 并支持服务器监控管理协议(IPMI), 实现与控制器上层接口的完全兼容.

|

图 3 特定场景优化后架构 |

2.2 系统总线

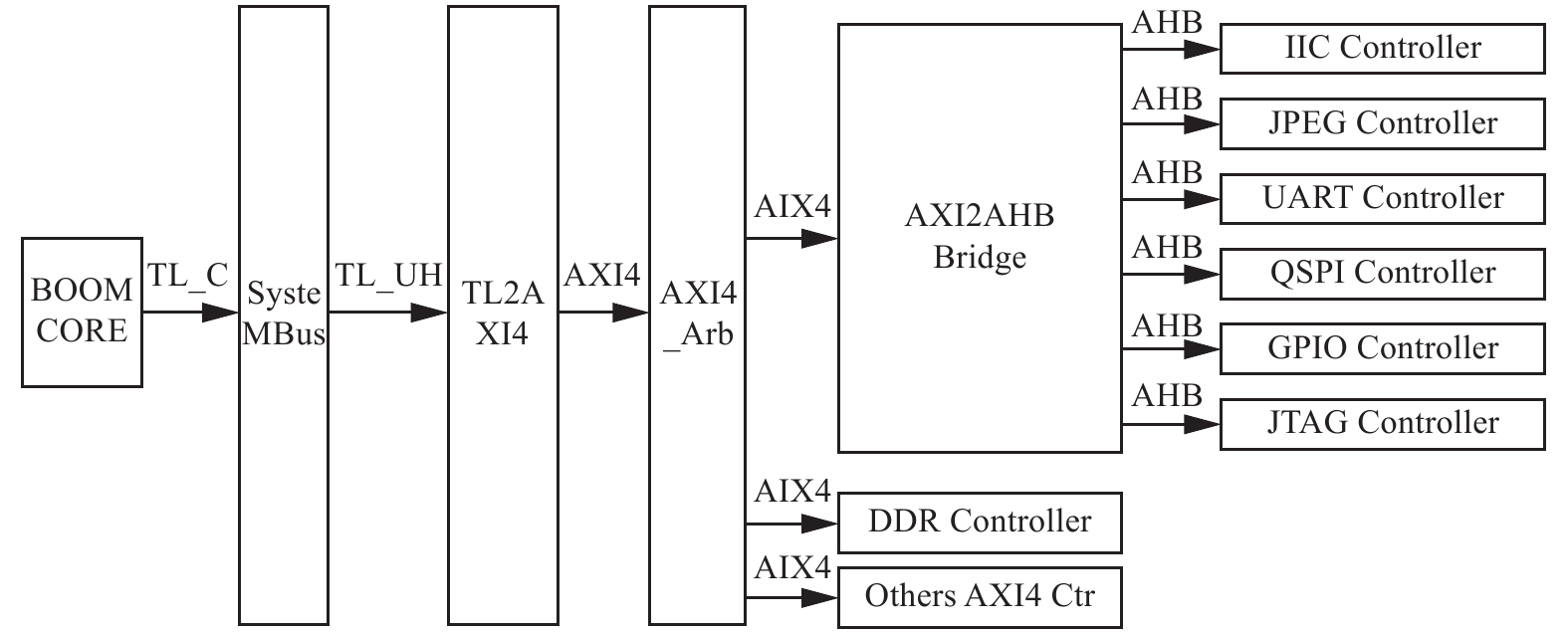

BOOM SoC使用的是TileLink总线协议, 该总线是加州大学伯克利分校设计的一种高速片上总线协议[10], 我们根据需求配置设计了TileLink转AXI4协议转换模块, 其总线互连和转换功能集中在SystemBus模块中, 详细功能模块划分如图4所示.

TileLink设计之初, 考虑了满足支持缓存一致性(cache coherence)协议, 并针对现有的多种一致性协议, 其将总线设计与协议设计相分离, 提高了TileLink总线的适应性.

TileLink总线的有向无环图结构主要是作为处理器的BoomTile, 可外接测控模块的FrontBus接口与MMIO_AXI4的外设接口、PeripheryBus外设接口、TLError和TLBroadcast的数据和控制交互. 其中主要包含了两部分功能:

1) TileLink网络拓扑实现, 包含了多主多从接口的Crossbar Agent、一从多主的Crossbar Agent和主从转换接口的Cache Agent实现.

2) TileLink协议转AXI4协议功能实现.

|

图 4 总线设计架构框图 |

2.3 地址空间与外设

根据服务器管理控制器外设需求, 我们对内部地址空间进行了划分, 如表1所示.

| 表 1 地址空间划分 |

2.4 固件与Linux内核

RISC-V内核启动过程中分为4部分: ZSBL、FSBL、BBL和Linux Core. 在启动过程中, 我们利用了Register存储空间的划分, 通过配置参数指定了各自的起始存储位置和大小, 启动程序可以读取并分析Register存储空间的配置参数, 获得FSBL、BBL和Linux Core在SD卡的存储位置和大小, 然后将其搬运到指定的DDR中运行.

基于改进的RISC-V 内核启动流程, 我们实现了对SD卡的坏块进行管理的设计. 通过Register配置空间可以任意指定ZSBL、FSBL、BBL和Linux Core的存储起始位置和大小, 如果SD卡某一块出现坏块, 可以通过配置Register配置空间的参数修改存储位置, 跳过坏块部分, 后期可以将Register配置空间的参数通过寄存器的方式存储在RISC-V处理器中, 可以在RISC-V处理器启动前通过外部进行配置启动参数. 上述坏块管理操作可以大大提高SD卡的可用性.

针对服务器管理控制器在人机交互上的便捷性需求, 我们移植了LXDE作为简洁易用的交互界面. LXDE是一款面向低功耗的轻量级桌面环境, 支持GTK特性, 用户界面更贴近Microsoft Windows 的菜单. 其在设计之初就考虑到了用户体验性与较低的资源占用, 注重模块化设计, 组件可以灵活增删, 满足了定制化需求, 也实现了以极低的内存与CPU负载承担功能丰富的桌面环境. 以上优点同时使其更容易移植在服务器管理控制器的系统上, 而且在低运行频率的FPGA原型平台上就可以进行安装调试.

在应用层, 我们集成了OpenBMC. OpenBMC由微软, 英特尔, IBM, 谷歌和Facebook发起, 是一个开源的软件架构, 其功能是用于打造一个完整可用的负责基板管理控制的Linux代码库. OpenBMC使用Yocto Project作为发布框架, 为移植提供了便利.

移植后使用浪潮自有的UI界面管理, 如图5所示.

|

图 5 服务器管理界面图 |

随着对OpenBMC的持续优化, 其已经能够实现带外的在线升级, 在不占用服务器网络带宽的情况下, 通过Web UI界面和软件包实现固件的刷新和维护工作. 通过提升OpenBMC的模块化、规范化程度, 将来可以为各类数据中心, 尤其是大规模、超大规模数据中心, 提供下一代开放技术管理方案.

3 控制器功能验证方法Boom-template工程集成了Verilator仿真环境. 在versim目录下执行make命令, 可以生成有关BOOM的simulator, 该simulator为一可执行文件, 名称为simulator-boom-system-BoomConfig, 可以执行任何RV64G的ISA测试, 包括单一测试用例以及整个测试集.

仿真环境的组成如图6, 其中MMIO AXI4和MEM AXI4接口分别接两块mem, DMI_debug port接SimDTM模块, 该模块负责产生仿真时的激励.

|

图 6 逻辑仿真示意图 |

SimDTM模块提供了C++与Verilog的接口, 由C++产生激励, 并通过驱动DMI_debug bus上的信号来驱动DUT, 从而完成仿真.

4 原型实现与验证 4.1 工程实现该系统基于Xilinx的Virtex Ultra Scale 440 FPGA进行了原型构建, 然后将整套系统从VU440移植到使用了Kintex-7系列的FPGA定制板卡上. Kintex-7系列FPGA实现了最佳成本/性能/功耗平衡, 芯片功能强大, 资源丰富. 其480T型号FPGA支持8通道PCIE接口, 提供了478K逻辑单元, 高达400个I/O口, 完全满足原型验证需求. 测试使用SD卡启动的方式实现逻辑代码的加载.

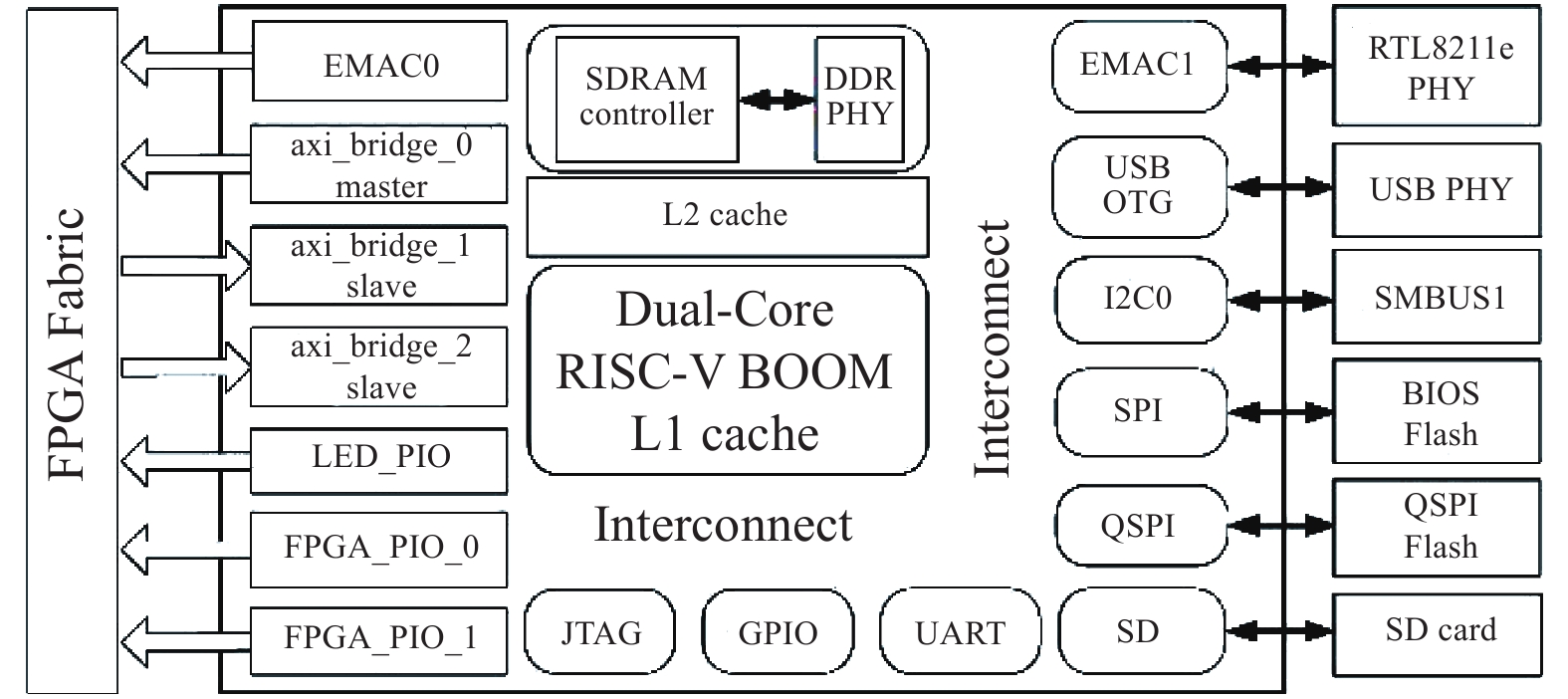

我们为FPGA原型系统开发了服务器管理控制器相关的外设模块, 如UART、Timer、SPI、外部存储、调试逻辑等, 结构如图7所示.

|

图 7 外围模块示意图 |

服务器管理控制器场景下RISC-V SoC的实现分两步: (1)基于BOOM多核的原型平台, 针对服务器管理控制器的各项需求进行扩展和优化, 集成外设接口, 进行稳定性和功能测试, 作为硬件研究和软件开发的基础平台. (2)将整套系统从VU440移植到FPGA定制板卡上, 如图8所示. 该定制板卡使用了Kintex-7系列XC7K480T芯片, 集成网口、串口等用于通信、调试的接口, 可通过PCIE接口连接服务器主板, 借此可以顺利进行上层移植以及功能性能测试.

|

图 8 测试板卡 |

4.2 FPGA原型调试

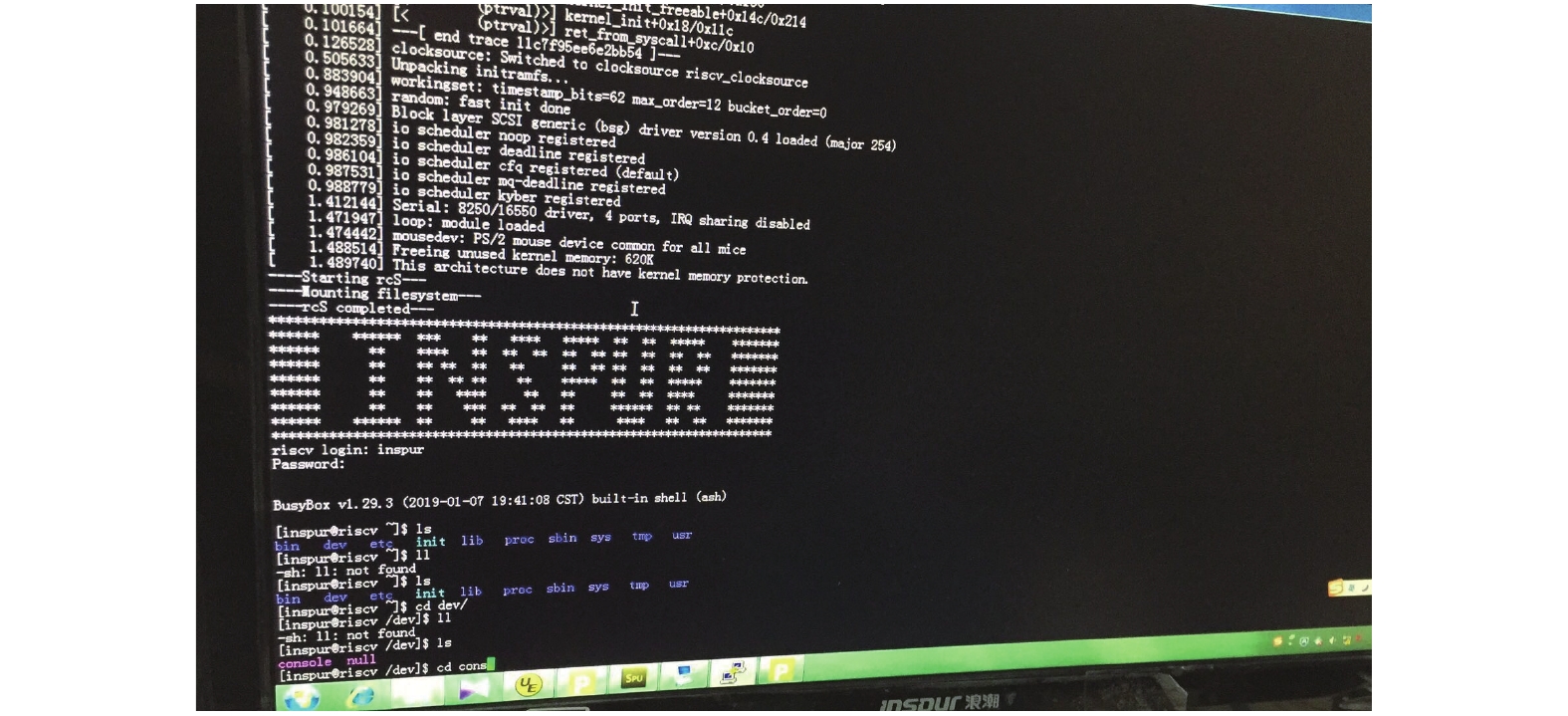

当设计从模拟实现到硬件实现时, 用户对系统当前状态的控制和理解会急剧下降. 为了帮助启动和调试低级软件和硬件, 在硬件中内置良好的调试支持至关重要. 当core运行操作系统时, 软件可以处理许多调试任务. 但是, 在许多情况下, 硬件支持至关重要. 我们重新制作了根文件系统以及相关组件, 增加了更多便于调试的命令, 启动界面如图9所示.

|

图 9 系统启动图 |

Debug系统debug host和RISC-V平台组成, 其中debug host包括运行调试器的调试主机(如笔记本电脑), 调试器经常使用的如GDB工具, 调试器通过调试转换器与调试传输硬件进行通信, 调试转换器模块可以使用OpenOCD, 其可以包括硬件驱动器, DTM为调试传输硬件, 即USB-JTAG适配器调试传输硬件将调试主机连接到平台的调试传输模块(DTM). DTM使用调试模块接口(DMI)提供对一个或多个调试模块(DM)的访问.

平台中的每个硬件线程都由一个DM控制. 硬件线程可能是异质的. 对硬件线程与DM之间的映射没有限制, 但通常单个core中的所有硬件线程都由相同的DM控制. 在大多数平台上, 只有一个DM可以控制平台中的所有硬件线程.

Program Buffer允许调试器在硬件线程上执行任意指令. 这种机制也可用于访问内存. 可选的系统总线访问块允许在不使用RISC-V Hart来执行访问的情况下进行存储器访问.

每个RISC-V可以实现触发模块(Trigger Module, TM). 当满足触发条件时, 硬件线程将停止并通知调试模块它们已停止.

DMI连接调试模块DM和DTM, 其中DTM是master, DM作为slave. 调试模块接口可以是具有一个主设备和一个从设备的普通总线, 或者是更全功能的总线, 如TileLink或AMBA高级外设总线. DMI使用7到32个地址位, 支持读写操作. 地址空间的开始段用于第一个DM, 额外空间可用于自定义调试设备、其他内核、附加DM等. 如果此DMI上有其他DM, 则DMI地址空间中下一个DM的基址将在nextdm中给出. 调试模块通过对其DMI地址空间的寄存器访问来进行操作.

4.3 性能测试在使用RISC-V BOOM搭建的服务器管理控制器FPGA原型系统上, 应用层的程序均可正常运行, 与上一代ARM架构原型系统相比, 该系统启动时间缩短15%.

我们对服务器管理控制器FPGA原型系统进行了软硬件测试和上层应用适配, 包括软件兼容性、系统稳定性、IO时延等参数, 优化后的系统可满足产品化的各项指标. 在进行各方面的适配后, 经Benchmarks基准测试, 系统性能测试分数超过ARM Cortex-A9, 具体性能如表2所示.

| 表 2 RISC-V Core 与ARM Cortex-A9 跑分对照 |

5 结语

本文首先对RISC-V的BOOM处理器进行了相关的扩展和优化, 并集成了服务器管理控制器所需外设, 移植了开源的上层应用框架, 构建了一套基于RISC-V处理器核的服务器管理控制器原型系统, 并进行了Benchmarks测试. 测试结果显示, 该系统处理性能优于ARM Cortex-A9处理器26%. 结果证明了RISC-V在面向具体应用场景上对ARM替代可行性.

| [1] |

Waterman A, Lee Y, Patterson D, et al. The RISC-V instruction set manual, Volume I: Base user-level ISA. Berkeley: EECS Department, University of California, 2011.

|

| [2] |

乔英良. 刀片服务器监控管理系统设计与实现[硕士学位论文]. 济南: 山东大学, 2012.

|

| [3] |

Celio C, Chiu PF, Nikolic B, et al. BOOM v2: An open-source out-of-order RISC-V core. Berkeley: EECS Department, University of California, 2017.

|

| [4] |

Celio C, Chiu PF, Asanović K, et al. BROOM: An open-source out-of-order processor with resilient low-voltage operation in 28-nm CMOS. IEEE Micro, 2019, 39(2): 52-60. DOI:10.1109/MM.2019.2897782 |

| [5] |

雷思磊. RISC-V架构的开源处理器及SoC研究综述. 单片机与嵌入式系统应用, 2017, 17(2): 56-60, 76. |

| [6] |

杨维科, 贺光辉, 景乃锋. 基于Rocket-Chip开源处理器的CNN加速模块的设计及实现. 微电子学与计算机, 2018, 35(4): 17-21. |

| [7] |

Rossi D, Conti F, Marongiu A, et al. PULP: A parallel ultra low power platform for next generation IoT applications. 2015 IEEE Hot Chips 27 Symposium (HCS). Cupertino, CA, USA. 2015. 1–39.

|

| [8] |

Collange C. Simty: Generalized SIMT execution on RISC-V. Proceeding of First Workshop on Computer Architecture Research with RISC-V (CARRV 2017). Boston, MA, USA. 2017.

|

| [9] |

苏振宇. 基于国产BMC的服务器安全启动技术研究与实现. 信息安全研究, 2017, 3(9): 823-831. DOI:10.3969/j.issn.2096-1057.2017.09.008 |

| [10] |

Celio C, Patterson D, Asanović K. The Berkeley Out-Of-Order Machine (BOOM): An industry-competitive, synthesizable, parameterized RISC-V processor. Berkeley: University of California, 2015.

|

2021, Vol. 30

2021, Vol. 30