近年来, 高性能的嵌入式系统层出不穷, 例如DSP, FPGA和ARM等众多硬件系统都得到了快速发展. 伴随着嵌入式系统的发展, 分布式计算系统以及数据交换协议和交换芯片也进入了快速发展期, 如RapidIO协议和以太网协议等在各种数据互联系统中发挥着重要的作用.

RapidIO协议具有传输速率快、基于硬件进行处理和低成本等特点. 它主要在嵌入式系统[1]的内部互联中发挥重要作用, 可以实现芯片和芯片, 板卡和板卡之间的相互连接, 如用于DSP之间和DSP板卡之间的互联并进行数据通信. IDT公司生产的交换芯片CPS1848[2]支持RapidIO2.0标准, 有48个双向的数据传输通路, 支持1x、2x或4x三种端口模式, 每个端口的速率可以设置为不同速率.

随着硬件设计的发展, 软件模拟硬件实现的仿真建模技术也得到快速发展, 例如时钟精确级的模拟和功能级的模拟等. SystemC[3]是一种新的系统建模语言, 其目的是为系统级设计提供一种单一的语言, 通过提供一个公共平台来更好地进行软硬件协同设计和验证. 其中集成的TLM2.0作为传输模型建模标准, 定义了通用数据单元payload, 十分适合进行RapidIO交换模型[4]的功能级模拟. 中国电子科技集团第三十八研究所设计研发的BWDSP芯片[5]是一款高性能数字信号处理器, 具有丰富的计算资源, 可以处理计算密集型任务. 故本文基于SystemC语言, 设计了用于多个BWDSP之间互联的RapidIO交换模型, 并且设计实现了BWDSP芯片构成的虚拟板卡平台, 使BWDSP芯片模型之间可以进行高效的数据传输.

本文的主要工作如下: 基于RapidIO协议特点和BWDSP体系结构特点, 设计了基于SystemC语言的RapidIO交换模型, 并且设计了多BWDSP芯片模型构成的虚拟板卡平台, 对虚拟平台的性能测试结果进行分析. 本文第1节介绍了RapidIO协议和BWDSP的体系结构; 第2节介绍了BWDSP虚拟平台的整体设计以及RapidIO交换模型的设计, 并且分析了BWDSP虚拟平台的工作流程和相关性能指标; 第3节对BWDSP虚拟平台的性能测试结果进行分析; 第4节是总结和展望.

1 RapidIO协议与BWDSP体系结构 1.1 RapidIO协议RapidIO协议作为一种快速数据交换协议, 具有总线频率高、延迟低和可靠性高等优点, 它可以为未来高性能的嵌入式系统发展提供数据交换和通信机制. RapidIO协议包括逻辑层、传输层和物理层3层[6]. 其中逻辑层定义了RapidIO组件使用的读写和消息传递语义; 传输层定义了RapidIO数据包如何通过RapidIO结构进行路由; 物理层定义了RapidIO链路的电路编码和电气特性. RapidIO架构主要由两种设备组成: 端点设备和交换机设备.

RapidIO协议是一种基于数据包交换的互联体系标准[7], 总体来说定义了请求包和响应包两种类型的包, 主要定义了维护包、读写包和消息包等数据包结构, 其中消息包又可以分为邮箱包和门铃包. RapidIO规范中定义了8种类型的数据包, 其类型如表1所示.

| 表 1 RapidIO数据包类型 |

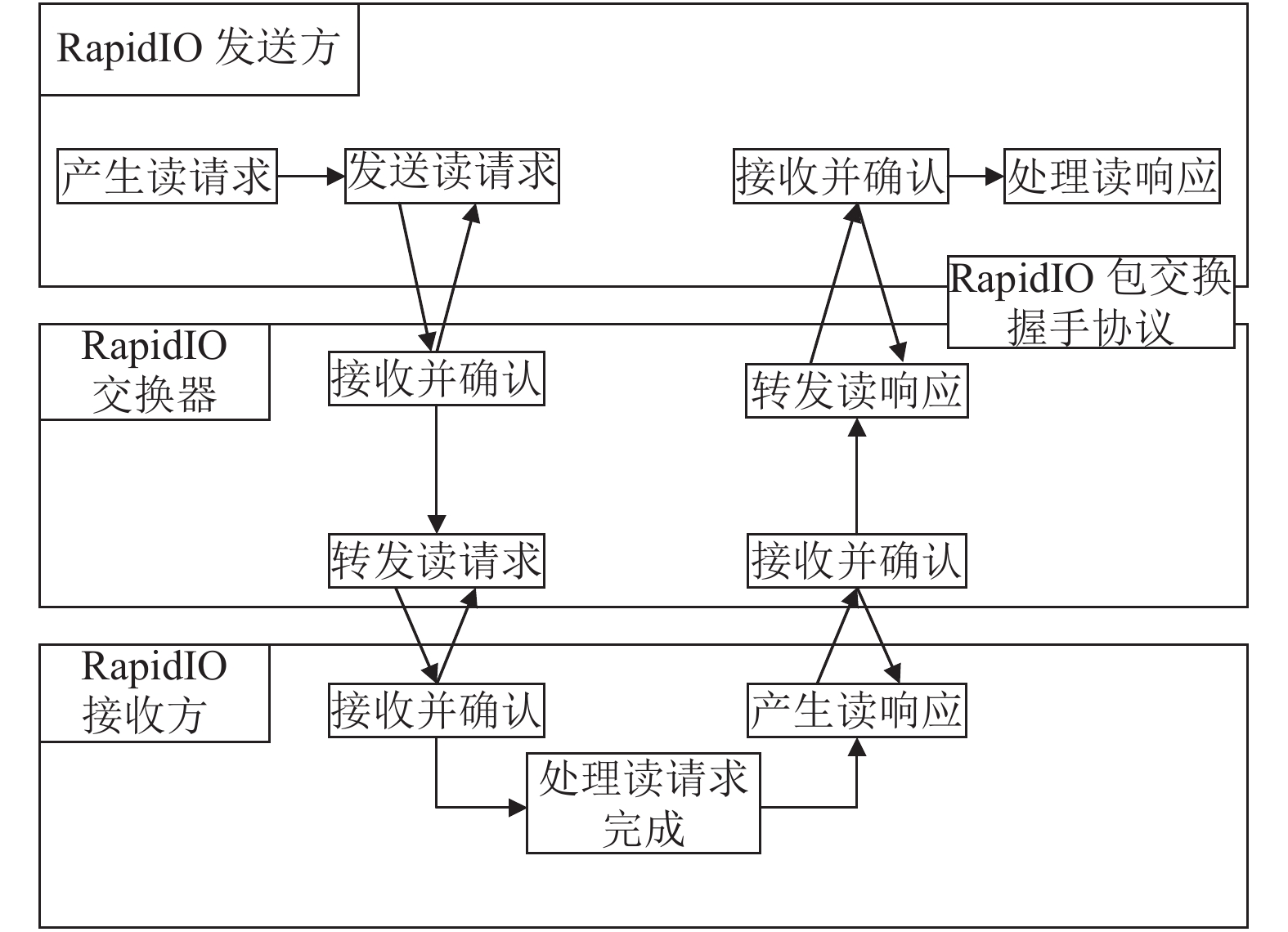

RapidIO的事务是通过数据包的传输来完成的[8]. 在每一个事务中, 发起方发出请求并产生相应的事务请求包, 事务请求包通过交换设备到达接收方, 在事务请求包收到来自接收方的响应后才会开始执行事务. RapidIO事务包在两个设备间传递时, 需要及时进行响应确认, 类似采用握手协议实现同步控制. RapidIO读响应包处理流程如图1所示.

|

图 1 RapidIO读响应事务处理流程 |

1.2 BWDSP体系结构

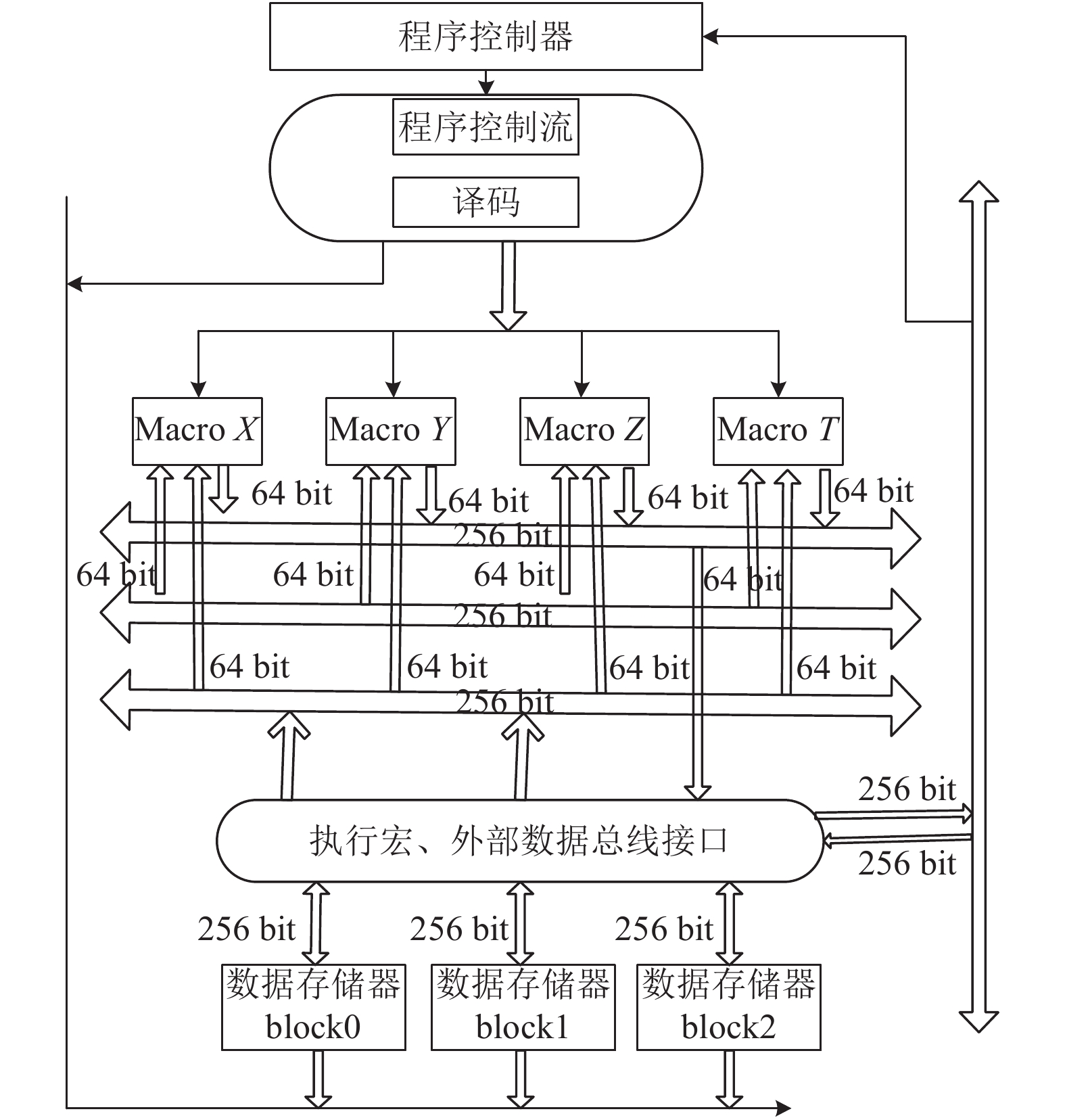

本文所采用的BWDSP模型是由中国电子科技集团第三十八所研制的BWDSP系列处理器, 可以对雷达信号进行快速处理[9], 是一种分簇架构设计的32位DSP处理器. 它同时兼容16位和32位的定点数据格式, 指令槽能够同时发射16条指令, 并使用SIMD和VLIW架构. BWDSP芯片的读数据和写数据总线位宽不同, 其中读数据位宽为512位, 写数据位宽为216位. BWDSP的最大工作主频为500 MHz, 指令周期为2 ns, 同时内部有11级的流水线. BWDSP体系结构中具有4个通用执行宏单元(计算簇)、3个地址产生器(U, V, W)和3个内存块(Block0, Block1, Block2), 每个执行宏间是彼此独立的高速链路口, 且每个执行宏可向其他3个执行宏传输数据. 每个计算簇与内存块、地址产生器间都通过总线相互连接. BWDSP的体系结构图如图2所示.

|

图 2 BWDSP体系结构 |

2 BWDSP虚拟平台设计

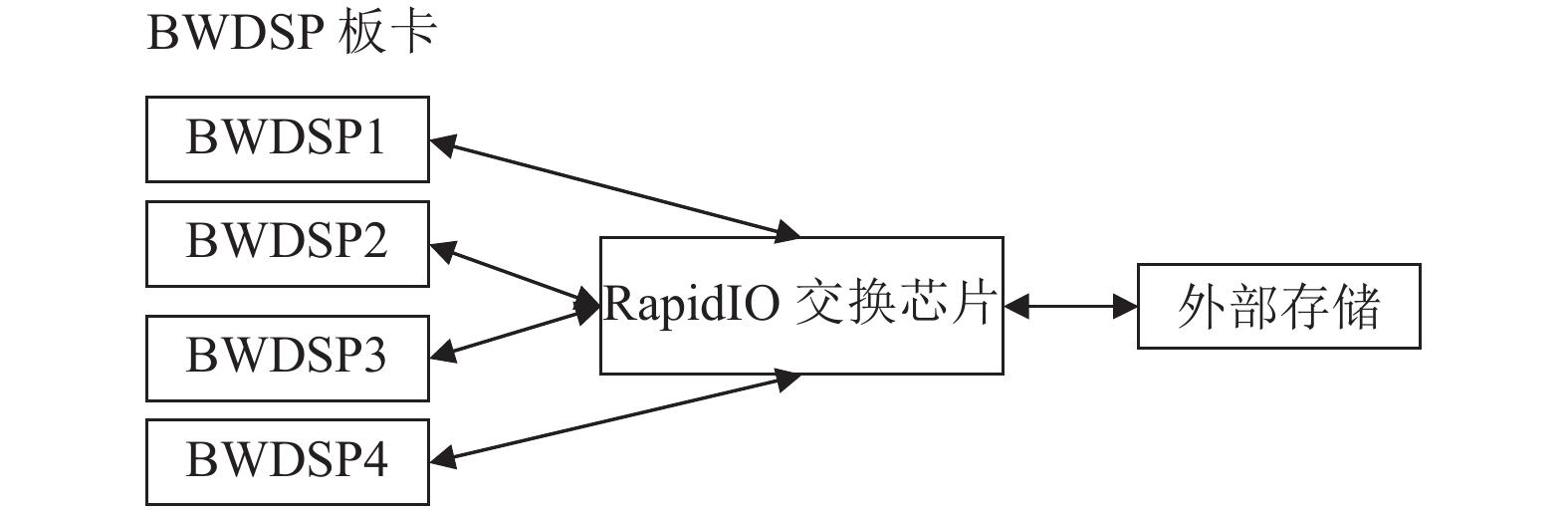

BWDSP板卡系统整体的设计是采取4片BWDSP模型与RapidIO交换机模型的4个端口相连接, 将交换机剩余的一个端口互联其他交换机模型或者外部存储模型, 如图3所示. 外部存储器模型可以是互联DDR等快速外设, 实现DSP对存储器中信息的快速读写. 外部存储器的地址空间映射到DSP地址空间中的某一块区域[10], 然后通过地址转换映射机制实现对外设中信息的读写, 通常使用DMA方式进行读写.

|

图 3 BWDSP板卡结构图 |

2.1 BWDSP虚拟平台数据流动

BWDSP板卡系统中, 4个BWDSP模型可以通过switch模型相互发送数据包, 数据包经过switch模型解析后会发送到正确的接收方BWDSP模型中. 由于在switch模型的各个端口设计了缓冲区, 各BWDSP模型同时发送数据时不会产生冲突阻塞问题. 当系统中数据流量在一定范围内, switch模型中不会发生缓存区溢出问题, 可以保持高效的数据转发速率[11].

在BWDSP虚拟平台中, RapidIO数据包是嵌入在TLM2.0标准定义的payload中进行传输的. RapidIO数据包在虚拟平台中的流动过程主要有如下几步:

(1) BWDSP模型根据事务要求生成相应的的RapidIO数据包.

(2) RapidIO数据包会被包装进payload中的数据属性中, 并在payload的扩展字段设置相应命令.

(3) Payload通过BWDSP模型的tlm_socket接口发出, 然后等待响应信息.

(4) RapidIO交换模型收到payload, 并将其存入内部的buffer缓冲区中, 采取存储转发模式, 同时向发送方响应交换模型收到该数据包.

(5) RapidIO交换模型从buffer中取出一个payload, 并从中解析出RapidIO数据包部分. 根据RapidIO数据包的类型和目标ID进行处理或转发.

(6) 如果该数据包有RapidIO模型进行处理, 则不需要转发操作. 否则, RapidIO交换模型根据目标ID查找路由表, 定位到某个出站接口.

(7) RapidIO交换模型从选择的出站接口转发该payload, 并等待下一个设备的响应确定是否从buffer缓冲区删除该payload.

(8) BWDSP模型接收到该payload后, 解析出其中的RapidIO数据包, 并根据事务要求进行处理, 再根据RapidIO数据包中的源设备ID进行响应, 发送一个响应数据包给发送方.

2.2 BWDSP虚拟平台功能特性BWDSP芯片最大工作主频500 MHz, 指令周期2 ns, 读总线位宽512 bit, 写总线位宽256 bit, 理论上读数据速率可以达到200 Gbs, 写数据速率可以达到100 Gbs, 完全可以处理RapidIO标准所定义的数据传输速率. 故BWDSP虚拟平台中RapidIO交换模型的数据处理速率应该达到RapidIO规范标准, 数据传输速率达到1.25 Gbs、2.5 Gbs和3.125 Gbs, 各个BWDSP模型之间可以进行快速通信.

BWDSP模型发送和接收的RapidIO数据包长度为len字节, 时钟频率为bw_fre, 总线的位宽bandwidth位. RapidIO交换模型的时钟频率rio_fre, 传输速率为rio_speed, 该模型每个时钟周期可以处理一个完整的RapidIO数据包. 理论上当BWDSP模型与RapidIO交换模型协同工作时, rio_fre和bw_fre应该满足式(1), rio_speed应该满足式(2).

| $rio\_fre = \dfrac{{bw\_fre \times bandwidth}}{{len \times 8}}$ | (1) |

| $rio\_speed = rio\_fre \times len \times 8$ | (2) |

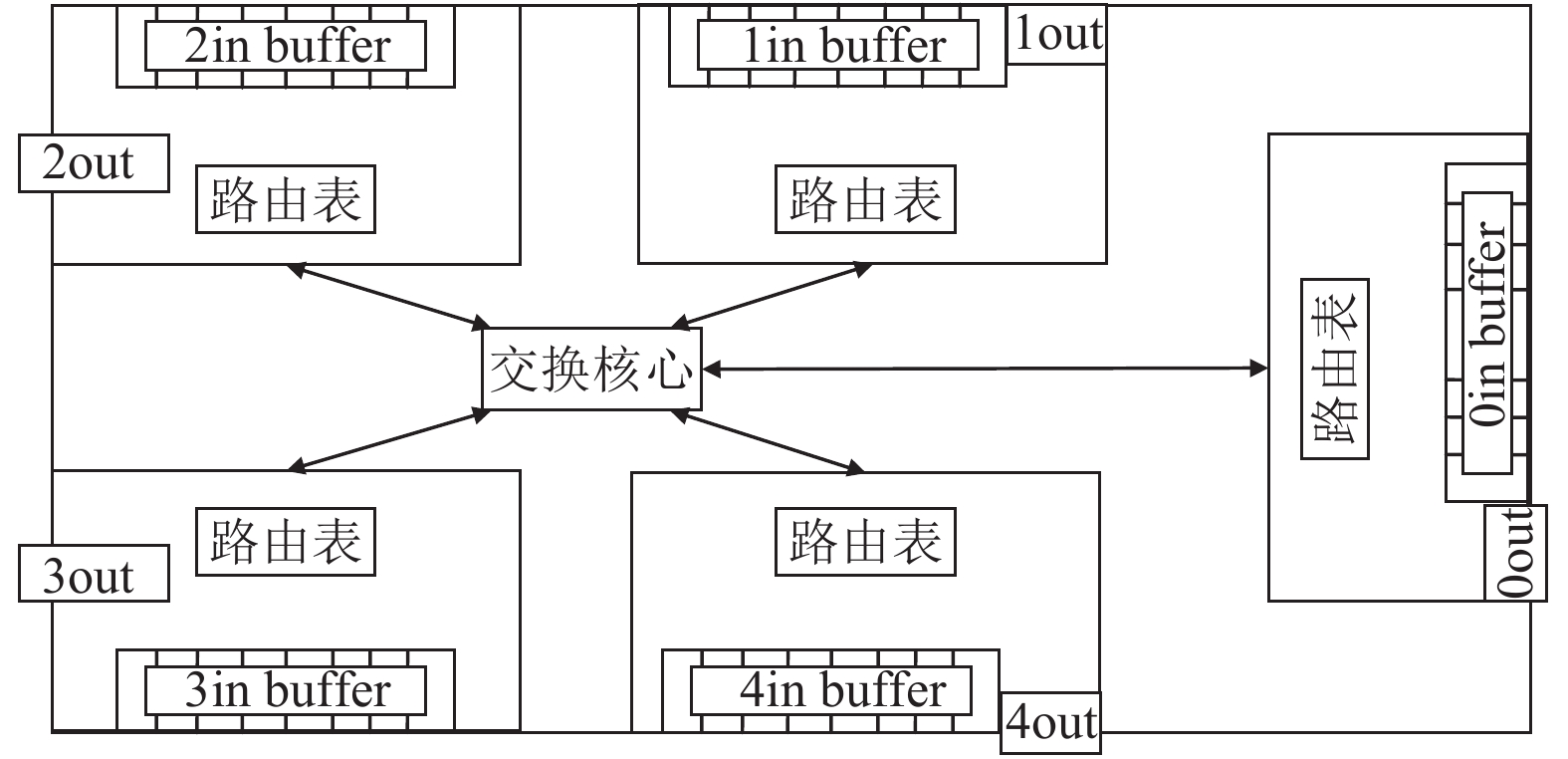

本文设计的BWDSP虚拟板卡中也含有4个BWDSP模型和一个RapidIO交换模型, RapidIO交换模型除了用于板内通信的接口以外, 还有一个离开板卡的接口来和外部板卡之间进行通信. 根据上述原则, 可设计如图4所示的switch功能模块, 一共有5个接口, 每个接口都有一个路由查询表和相应的入站/出站模块. 其中, 0号接口负责外部板卡和存储设备的通信, 第1、2、3和4号接口分别与板卡内部的4个BWDSP芯片模型相连.

|

图 4 RapidIO交换模型结构图 |

RapidIO交换模型的工作方式为存储转发模式, switch的设计中为每个端口保留一个缓冲队列, 设计为8个缓冲单元, 每个switch模型有5个端口, 按每个缓存单元为RapidIO数据包最大长度276字节计算, 为276×8×5字节. 该类初始化时通过参数设置来初始化其各个端口, 并且初始化各端口相连的buffer缓冲区. 同时设计路由表基类Route_table类作为switch类的模板参数, 在switch模型初始化的同时实例化特定的路由表, 使switch类的设计具有一定的扩展性, 可以兼容新的路由表结构设计.

路由表的基本工作原理如下: 从输入分组中提取目的地ID字段并将其与可编程路由表中的值进行比较并转发. 本系统的RapidIO交换机为每个交换机端口设计了一个单独的路由表, 因此每个接口都可以不同地路由数据包, 根据数据包的目标ID字段中的值与路由表中编程的值之间的比较, 将传入数据包路由到其目标接口. 数据包可以路由到以下目的地之一: 单播到某一接口, 终端设备或者switch设备; 多播到多个接口[12].

2.4 BWDSP虚拟平台初始化BWDSP虚拟平台初始化时, 首先需要进行RapidIO系统的初始化, 该阶段有一个初始化枚举探测阶段, 用于探测整个系统的拓扑结构并且分配终端设备ID. 该功能主要由系统中一个或多个终端设备加载系统初始化驱动程序代码, 作为主设备开始执行系统探测功能, 本设计中将初始化设备ID分配为0的终端节点当作为主设备开始执行系统枚举探测. 系统中各switch路由表的初始化有静态配置和动态配置方式[13]. 静态配置通常是通过系统上电初始化I2C等方式进行配置, 动态配置则是在系统枚举探测时, 分配各个设备ID的同时将路由信息写入RapidIO交换模型的路由表中, 同时设置默认路由端口信息.

RapidIO的系统初始化探测算法采用类似于深度优先的图搜索算法[14, 15], 在搜索过程中会形成一颗搜索树, 该搜索树即可代表整个系统设备互联的拓扑结构图. RapidIO系统初始化探测算法如算法1所示, 其中rioEnumerateNeighbor函数实现深度优先搜索部分.

算法1. RapidIO系统初始化探测算法

输入: BWDSP芯片和RapidIO交换模型组成的BWDSP虚拟平台系统

输出: BWDSP虚拟平台系统拓扑结构和各交换模型路由表信息

1)初始化时global_id=0,hop_count=0, 所有终端设备的base_id设为0xff

选择某片BWDSP模型作为主设备, 分配base_id为0x00

由该主设备执行rioEnumerateNeighbor(hop_count)算法

2) rioEnumerateNeighbor(hop_count)算法流程:

发送跳数为hop_count的初始化维护数据包, 然后等待响应信息(调用read_information()函数实现)

if收到终端节点的响应, 且该终端节点未被锁定

global_id++

分配global_id为该终端设备的base_id(调用write_information()函数实现)

算法返回

else if收到终端节点的响应, 且该终端节点已经被锁定

则该终端设备已经分配base_id, 放弃分配

算法返回

else if收到switch节点发回的响应信息

提取响应信息数据负载中switch端口数总数port_total和与该设备相连的switch端口信息port_number

通过一个for循环将所有已检测到的设备id即0-global_id和port_number作为路由信息写入该响应switch(调用write_information()函数实现)

while(port_total-1) //将port_number端口去掉, 防止重复检测

记录此时检测的switch端口号为port_numvar

递归执行rioEnumerateNeighbor(hop_count+1)算法, 并等待算法返回结果

将新检测到的所有设备id信息和port_numvar作为路由信息写入该switch中

算法返回

假设该系统中每个BWDSP板卡结构都如图3所示, RapidIO交换模型用于互联各BWDSP板卡, 系统中有N个BWDSP芯片和M个RapidIO交换模型, 其中N为4的整数倍, N和M的关系近似为N=3×M. 采用单主机进行系统初始化, 则主机到各终端设备路径长度近似为log4N. 需要读取一次设备信息, 并且写一次设备ID信息到终端设备中, 同时写一次路由信息到相应的RapidIO交换模型中, 故时间上限为3×(N–1)×log4N, 时间复杂为O(N×log4N). 每次发送数据包都是由主机进行发送的, 所以需要的存储量为每个RapidIO交换模型保留一个RapidIO数据包.

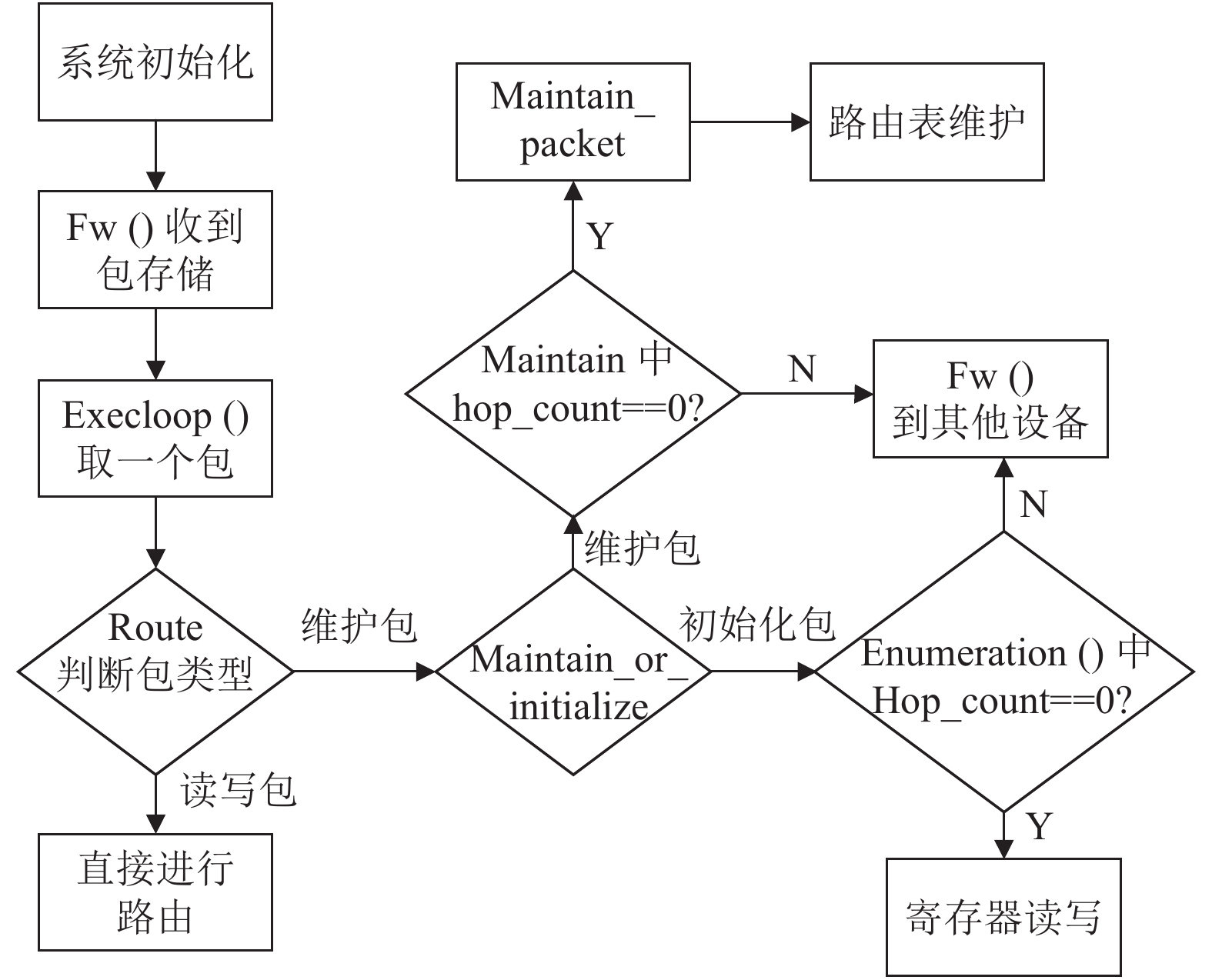

2.5 BWDSP虚拟平台工作流程图5是BWDSP虚拟平台运行流程图, 从系统启动时RapidIO系统初始化探测枚举阶段开始, 到系统正常工作时BWDSP模型之间通过swtich模型进行相互通信. 图5是以RapidIO交换模型的工作视角为主体进行展示的, 故其工作流程是对RapidIO数据包的解析和转发, 同时对寄存器读写和路由表维护信息进行简单展示.

BWDSP虚拟平台启动后[16], 首先会初始化终端设备和交换机设备中的各个寄存器, 并且选择其中一个终端设备将其base_id设为0, 使其成为主设备. 然后, 由主设备开始进行系统初始化阶段的探测枚举阶段, 该阶段主要是探测并获得整个系统的网络拓扑结构, 并且给各switch中的路由表动态配置路由信息. 当整个系统初始化阶段结束以后, 各个BWDSP模型之间可以相互发送信息, 通过RapidIO交换模型进行数据的交互, 协同完成某项工作. 系统初始化结束之后, 主设备拥有整个系统的拓扑结构信息, 可以提取该信息并保存.

|

图 5 BWDSP虚拟平台运行过程 |

3 BWDSP虚拟平台实验和分析 3.1 系统传输速率分析

对普通数据读写包的发送进行测试, 将数据发送设备和交换机设备的频率都设置为2 MHz, 数据接收BWDSP保持在正常的500 MHz工作频率下. 根据上文式(1)和式(2), 当RapidIO数据包长度取276字节时, RapidIO交换模型在1 s内转发处理的数据字节数为(256+20)×2 MB, 速率近似为4.416 Gbs. 然后又测试了发送不同RapidIO数据包长度时, 系统整体的传输速率, 如数据字节数为(64+20)×2 MB时, swtich模型的速率近似为1.344 Gbs. 实验结果表明, 该BWDSP虚拟平台中交换模型的数据传输速率符合RapidIO规范标准中的传输速率. 表2是在不同数据包长度下, RapidIO交换模型的传输速率测试结果.

表2中第1条和第2条测试数据中数据包长度字节为36 B和52 B时, 发送设备采用固定的发送频率进行数据发送. 此时交换设备和接收设备无法充分利用信道和计算资源, 数据传输速率分别是0.576 Gbs和0.832 Gbs.

| 表 2 数据传输速率表 |

3.2 系统初始化阶段分析

RapidIO系统初始化阶段主要是进行系统的探测枚举, 即枚举整个系统中的所有设备, 并分配终端设备base_id和配置各交换机路由表. 本文在设计时对RapidIO初始化阶段数据包采取直通转发, 这是为了加快系统初始化, 故我们采取对传输数据包的长度和个数进行统计, 并近似算出系统初始化阶段时间, 与理论时间进行对比分析. 设BWDSP虚拟平台中BWDSP模型数为bw_num个, switch模型数为sw_num个, 初始化阶段发送数据包数为pkt_num个. 则系统初始化时间下限为t_lower, 上限为t_high, 下限和上限分别符合式(3)和式(4).

| $t\_lower = pkt\_num \times \dfrac{1}{{rio\_fre}}$ | (3) |

| $ t\_high = \left( {pkt\_num + sw\_num} \right) \times \dfrac{1}{{rio\_fre}} $ | (4) |

系统初始化枚举探测阶段执行完成时, 通过打印输出来检查各switch模型的路由表, 与系统理论拓扑结构保持一致, 说明系统初始化阶段枚举探测算法正常工作. 表3所示是在不同系统拓扑结构下, BWDSP和交换机模型的频率都设置为2 MHz时, BWDSP系统初始化时发送的数据包个数.

| 表 3 初始化数据包数 |

表3中BWDSP模型数为20和switch模型数为6进行分析, 系统发送的RapidIO数据包的数量为434, 系统时钟频率为2 MHz, 发送数据包时间为217 us. 对于最后一个发送数据包被接收时, 理论上所经过的switch模型个数少于BWDSP模型数, 故系统初始化阶段需要时间下限为217 us, 上限为227 us. 当系统拓扑结构更大时, 初始化阶段发送的数据包数量也会相应增加, 上述时间计算公式依然适用.

表3中第5条和第6条实验数据具有相同BWDSP模型数和switch模型数, 但是系统拓扑结构互联方式不同, 导致系统初始化时需要的数据包数量也不相同. 在两种系统拓扑结构下, RapidIO初始化功能都可以正确执行, 设计的BWDSP虚拟平台具有一定的可扩展性.

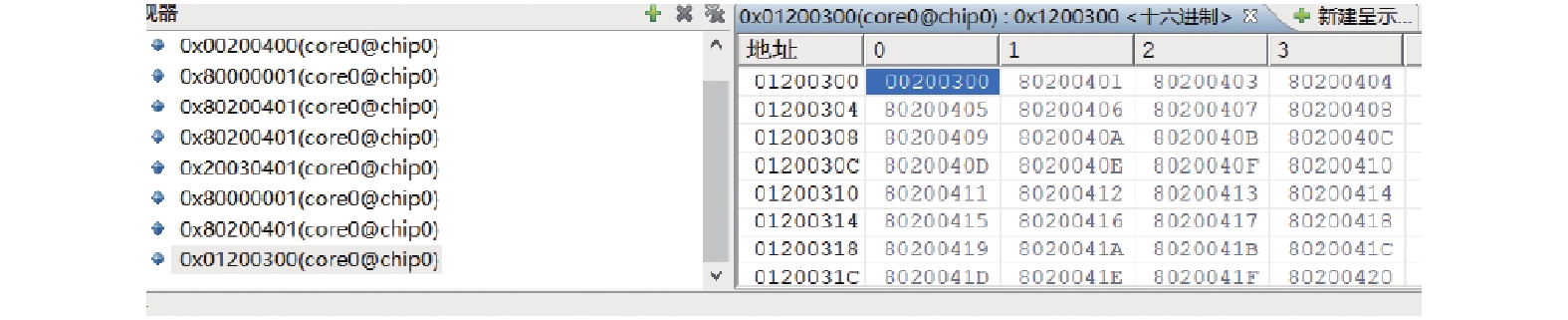

3.3 系统功能正确性分析中国电子科技集团第三十八研究所设计了用于软硬件模型开发和调试的CES集成开发环境, 本文设计的BWDSP虚拟板卡平台使用三十八所的CES集成开发环境进行调试. BWDSP主设备模型会向RapidIO交换模型相连的存储模型中指定位置写入数据, 该数据包会通过switch模型进行转发, 然后检查该位置数据是否写入正确, 以此验证RapidIO交换模型能否对数据包进行正确转发. 实验中BWDSP模型向存储位置为0x012003001位置写入0x80200401, 然后逐个位置写入加1后的值, 测试结果如图6所示. 该测试结果表明该RapidIO交换模型可以正常工作, 将RapidIO数据包转发到正确设备和地址并进行处理.

|

图 6 数据传输测试结果 |

RapidIO协议中其他的数据包类型如维护数据包等, 都进行了相应的数据通信测试[17], 并且测试结果正确, 符合RapidIO规范标准. 如路由信息维护数据包的测试结果, 成功将switch模型中的路由信息修改为维护数据包中数据负载部分, 正确实现了switch模型的路由表信息动态维护功能.

3.4 系统延迟性分析BWDSP虚拟平台正常工作时, 即各个BWDSP模型之间进行数据传输时, 通过实验测量数据传输延迟时间, 对BWDSP虚拟平台传输性能进行分析.

表4中的数据包长度为276字节, 传播时延信息是发送方结束发送时刻到接收方开始接收时刻之间的时间, 单位为us. 各个BWDSP芯片同时通过RapidIO交换模型进行数据发送, 并且是随机发往其他设备, 故传播时延并非是单个数据包传播时延乘以包的数量. 其中第5条和第6条实验数据的传播时延也说明了系统的拓扑结构会影响BWDSP芯片之间的数据传输. 结合终端设备频率和读写位宽信息, 可以得知数据发送时间和接收时间为20 us. 完整的数据传输时间tm如式(5)所示, 其中tp是传播时间, ts是发送数据时间, tr是接收数据时间.

| $tm = tp + ts + tr$ | (5) |

| 表 4 数据传输时延表 |

当系统中数据流量[18]过大时, 测试RapidIO交换模型发生缓存数据溢出时的系统行为. 该RapidIO交换模型检测到缓存溢出情况, 立刻向数据的发送方进行缓存已满的响应, 并减缓数据发送方的数据发送频率, 调整系统的拥塞程度.

3.5 实验总结Tundra公司开发的RapidIO交换芯片Tsi578应用广泛, 符合1.3版本的串行RapidIO互联规范, 串行数据传输速率可以达到1.25 Gbs. 而本文所设计的RapidIO交换模型除了正常工作的5端口模式外, 支持扩展端口数, 可以灵活配置形成复杂的系统拓扑结构. 采用RapidIO最大数据包长度276字节时, 数据传输速率可以达到4.416 Gbs.

BWDSP芯片计算峰值性能为12.8 GFLOPS, 则4个芯片构成的BWDSP板卡系统在忽略系统通信消耗的情况下, 理论计算性能可以达到51.2 GFLOPS, 具有进行深度学习应用开发的潜力.

综合上述实验结果及分析, 该BWDSP虚拟平台成功实现了多BWDSP模型之间的数据通信, 且数据传输速率符合RapidIO标准规定.

4 总结与展望为了使RapidIO协议更好的适用于具体硬件产品, 提高BWDSP模型之间相互通信的能力. 本文以国产BWDSP芯片模型为基础, 基于SystemC建模语言设计了RapidIO交换模型, 并构建了BWDSP虚拟平台. 实验结果表明该串行RapidIO的功能级模拟符合实际RapidIO规范标准, 设计的BWDSP虚拟平台数据传输速率达到预先设计的性能指标.

本文BWDSP虚拟平台中的交换模型主要实现串行RapidIO功能级的模拟, 在switch交换模型内部的调度算法模块中, 目前只实现了按照时间和优先级的轮询调度方式, 考虑为BWDSP虚拟平台提供更加复杂的数据包调度方式以适应多种数据通信应用场景. 未来针对更加复杂的系统互联拓扑结构, 需要设计更加灵活的动态路由算法, 优化数据传输性能.

| [1] |

胡阳. 基于PowerPC的嵌入式无线通信控制单元设计[硕士学位论文]. 北京: 北京邮电大学, 2015.

|

| [2] |

Ma YK. Design on SRIO bus switch module based on CPS1848. Radio Engineering, 2014, 44(10): 73-76. |

| [3] |

李挥, 陈曦. SystemC电子系统级设计. 北京: 科学出版社, 2010.

|

| [4] |

Yang CX. Design and implementation of switch unit in communication system based on RapidIO bus. Computer & Digital Engineering, 2014, 42(6): 1003-1010. |

| [5] |

邓文齐. 基于BWDSP的众核深度学习加速器的研究[硕士学位论文]. 合肥: 中国科学技术大学, 2018.

|

| [6] |

Gao YG, Wang H, Ni M. Design of serial RapidIO-PCI bridge based on FPGA. Computer Engineering, 2009, 35(2): 233-235. |

| [7] |

Wu CR, Cen F, Cai HZ. A high-performance heterogeneous embedded signal processing system based on serial RapidIO interconnection. Proceedings of the IEEE International Conference on Computer Science and Information Technology. Chengdu, China. 2010. 611–614, doi: 10.1109/ICCSIT.2010.5564987.

|

| [8] |

Liu J, Tian Y, Wei H, et al. Design and implementation of serial RapidIO based on DSP and FPGA. Advanced Materials Research, 2014, 971–973: 1581-1585. DOI:10.4028/www.scientific.net/AMR.971-973.1581 |

| [9] |

王凤驰, 陈常青, 李正东. 基于“魂芯一号”的雷达信号处理机边扫设计. 雷达科学与技术, 2014, 12(6): 645-648. DOI:10.3969/j.issn.1672-2337.2014.06.015 |

| [10] |

Huang L, Liu FY. High-speed interconnection network based on RapidIO and memory mapping. Computer Engineering, 2008, 34(14): 116-117, 120. |

| [11] |

Shah SA, Khanvilkar S, Khokhar A. RapidIO traffic management and flow arbitration protocol. IEEE Communications Magazine, 2006, 44(7): 45-52. DOI:10.1109/MCOM.2006.1668380 |

| [12] |

Deng B, Zhang YS. Resaerch on RapidIO multicasting configuration and transfer performance. Aeronautical Computing Technique, 2016, 46(3): 111-115. |

| [13] |

Huang ZP, Wu G, Cui WL. Technology of RapidIO concurrent static routing enum. Modern Radar, 2017, 39(9): 16-19. DOI:10.16592/j.cnki.1004-7859.2017.09.004 |

| [14] |

刘萍, 冯桂莲. 图的深度优先搜索遍历算法分析及其应用. 青海师范大学学报(自然科学版), 2007(3): 41-44. |

| [15] |

殷从月, 张兴明, 魏帅, 等. RapidIO网络中一种基于最小隔离块的流量驱动机制. 计算机工程, 2018, 44(9): 118-123, 135. DOI:10.19678/j.issn.1000-3428.0049197 |

| [16] |

Huang ZZ, Chai XL, Li X, et al. Driver design of PCI-RapidIO bridge based on vxworks. Computer Engineering, 2010, 36(4): 239-240, 243. |

| [17] |

Rao K. Test and analysis of serial RapidIO system based on DSP and FPGA. Information and Electronic Engineering, 2012, 10(6): 680-684. |

| [18] |

Zhang Y, Wang Y, Zhang P. Research on physical layer traffic management schemes in serial RapidIO interconnect. The Journal of China Universities of Posts and Telecommunications, 2011, 18(1): 64-69. DOI:10.1016/s1005-8885(10)60029-5 |

2020, Vol. 29

2020, Vol. 29