# 改进中值滤波方法的图像预处理技术<sup>©</sup>

王红君<sup>1</sup>, 施 楠<sup>1</sup>, 赵 辉<sup>1,2</sup>, 岳有军<sup>1</sup>

1(天津理工大学 天津市复杂系统控制理论与应用重点实验室, 天津 300384) 2(天津农学院, 天津 300384)

摘 要: 图像实时处理系统日益发展, 这无疑对 FPGA 的广泛应用提供了良好的平台. 针对在某些领域传统的中 值滤波算法无法快速有效的对采集到的图像进行处理, 采用改进中值滤波利用 FPGA 运行速度快、内部程序并行 运行等优点,设计出具有高实时性、高灵活性的图像预处理系统. 通过中值滤波算法特点运用 Verilog 硬件描述语 言进行代码编写、并在 Quartus II、Modelsim 进行实现仿真、最后与 MATLAB 中值滤波仿真图及多级中值滤波进 行对比,得出利用 FPGA 处理改进中值滤波不但能够顺利对图像进行中值滤波,而且具有运算速度快、低能耗的 特点.

关键词: 图像实时处理; 图像预处理; 中值滤波; FPGA

#### **Image Preprocessing Technology Based on Improved Median Filter**

WANG Hong-Jun<sup>1</sup>, SHI Nan<sup>1</sup>, ZHAO Hui<sup>1,2</sup>, YUE You-Jun<sup>1</sup>

<sup>1</sup>(Tianjin Key Laboratory of Control Theory & Applications in Complicated Systems, Tianjin University of Technology, Tianjin 300384, China)

<sup>2</sup>(Tianjin Agricultural University, Tianjin 300384, China)

Abstract: The development of image real-time processing system has brought a good platform of the widespread use of FPGA. Aiming at the problem that traditional median filter algorithm cannot process collected images quickly and efficiently, this paper adopts improved median filter and makes use of advantages, such as fast running speed, parallel running of inner program, to design an image preprocessing system with high real time ability and high flexibility. Using the features of median filter and Verilog hardware description language to code. And then realize simulation in Quartus II and Modelsim. At last, compared with MATLAB median filter simulation figure and multilevel median filter, it has shown that using FPGA to process and improve median filter can not only conduct median filter to images successfully, but also has the ability of fast operation speed and low energy consumption.

Key words: image real-time processing; image preprocessing; median filter; FPGA

数字图像处理现在被广泛应运于很多领域, 其原 因是因为在图像信息采集及图像信息传输过程中由于 会遇到噪音、光照、传输设备不稳定等环境或人为因 素,导致图片模糊、畸变质量下降的情况出现[1-3].即 为了还原图像的清晰度和图像质量就必须对图像进行 处理. 中值滤波是一种简单且效果很好的滤波方法, 能够有效的去除图像中噪音带来的干扰并且保留图像

的清晰度.

FPGA 技术正处于高速发展的时期,新型芯片的 规模越来越大, 成本也越来越低, 低端的 FPGA 已经 逐步取代了传统的数字原件, 高端的 FPGA 不断在争 夺 ASIC 的市场份额。大容量、低电压低消耗、高集成、 高效率这些都是 FPGA 能够在实时性较高的图像处理 系统中发挥作用的可靠保障[4-6].

Research and Development 研究开发 237

① 基金项目:天津市农业科技成果转化与推广计划(201203060);天津市科技计划(13TXZYJC43000) 收稿时间:2014-08-26;收到修改稿时间:2014-10-13

早期 Nieminen 和 Neuvo 提出了"多级中值滤波",这种方法能够有效提高滤波效果,但在噪声干扰不是很大的情况下其去噪能力与传统算法差别不大,虽然能够减少处理时间可是不能达到很高的实时效果<sup>[7-10]</sup>.本文采用的改进中值滤波算法,利用 FPGA 设计出高效率、低能耗的图像预处理系统.

#### 1 中值滤波及改进算法原理

#### 1.1 中值滤波

中值滤波可以有效地解决噪声所带来的图像质量下降问题,去除噪声还原图像清晰度也可以线性滤波的算法,但由于大多数线性滤波算法都具有低通性,在去除噪声的同时也会导致图像边缘模糊,而中值滤波属于非线性滤波算法,不但可以有效去除噪声而且可以保护图像边缘[11].

中值滤波的算法:选择一个具有奇数像素点的窗口 X, 把图像在这个窗口上的像素进行扫描, 将此窗口中扫描的像素点按灰度值大小进行排列, 最后用排列中最中间的灰度值取代窗口中心的灰度值. 中值滤波定义如下:

一组数  $x_1, x_2, x_3, \dots, x_n$ , 把其中的数按大小排列:

$$x_{i1} \le x_{i2} \le x_{i3} \dots \le x_{in} \tag{1}$$

$$y = Med(x_1, x_2, x_3, ..., x_n) = \begin{cases} x_{i(\frac{n+1}{2})} & \text{n为奇数} \\ \frac{1}{2} \left[ x_{i(\frac{n}{2})} + x_{i(\frac{n+1}{2})} \right] & \text{n为偶数} \end{cases}$$

(2)

y 为这组数中的中值,例如有一组灰度值(20,60,90,100,40)按照大小排列后得出其中值位 60.这种思想很容易应运到二维空间,也就是选取某种大小的二维窗口进行像素扫描.设 $\{x_{ij},(i,j)\in X^2\}$ 表示图像各点的灰度值,滤波窗口的二维滤波可定义为:

$y_{ij} = Med\{x_{ij}\} = Med\{x_{(i+s),(j+t)}(s,t) \in B, (i,j) \in X^2\}$  (3) 一般为了中值滤波便于实现,我们用 3x3 的采集窗口,实现过程如下所示.

238 研究开发 Research and Development

从小到大排列

7 7 8 14 23 24 56 59 95

用中值替换中间灰度值

55 75 26 15 95 41 25 36 15 46 24 3 24 26 4 28 8 56 23 2 45 69 98 47 36 45 12 36 5 14 23 24 26 58 12 46 58 16 2 20 51 10 7 59 7 42 78 54 90 35 33 21

图 2 中值滤波后灰度值

替换后的灰度值将参加下一步的中值滤波,直到完成所有像素点的滤波算法.

#### 1.2 改进中值滤波

一般窗口扫描图像像素值是由左到右,由上到下的顺序进行的.利用传统的中值滤波以 3x3 窗口处理一幅 256x256 大小的图像,将会有 65536 个像素值进行运算,而每一个像素值则需要比较 36 次.如此庞大的运算量显然在一些实时性要求较高的领域是无法满足的.由于本文采用 FPGA 进行图像处理,所以可以利用 FPGA 的并行处理更好的完成中值滤波.

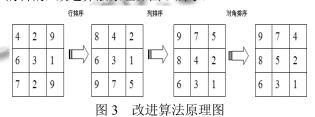

这里采用一种快速的中值滤波算法,这种算法不 是利用将某像素点及其周围灰度值的大小进行大小排 列找出中值,而是充分利用排序算法的实质,以最快 的速度找出中值且排除其他非中值,以达到提高效率 的目的. 改进算法原理如图 3 所示.

为了更好的说明算法原理,设 3x3 窗口中的像素值分别为 R11, R12, R13, R21, R22, R23, R31, R32, R33.

算法实现排序比较过程:另 max 为比较灰度值中的最大值,min 为最小值,mid 为中值,max\_min 为三个最大值中的最小值,min\_max 为三个最小值中的最大值,mid\_mid 为三个中值中的中间值,med\_out 为输出中值。

第 1 步: 分别比较 3x3 窗口中每行的灰度值, 按

降序排列, 取最大值的过程为 max1 = max{ R11.R12.R13 },  $\max 2 = \max \{ R21, R22, R23 \}, \max 3 = \max \{ R31, R32, R33 \};$ 中 值 的 过 程 为 mid1 = mid{R11,R12,R13}, mid2 = mid{ R21,R22,R23 }, mid3 = mid{ R31,R32,R33 }; 取最 小值为 min1 = min{ R11, R12, R13 }, min2 = min{ R21, R22, R23 },  $min 3 = min \{ R31, R32, R33 \}$

第2步: 将比较后的灰度值重新按照降序排列分 别放入每一列,第一列为每一行的最大值,找出最小 值 max\_min,由于最大值中的最大值肯定是所有像素 点的最大值, 而第二行的最大值肯定大于该行以及下 一行的所有像素点, 所有将第一列的前两个点剔除. 同理求出 mid mid, min max.

第3步: 将上一步求得的三个数进行比较也就是 扫描窗口对角线像素点进行比较最后求出中值 med\_out

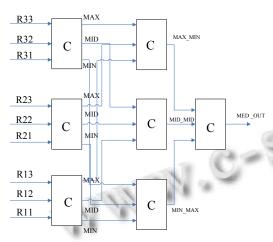

像素数据在传输处理的同时扫描窗口也在不停 的改变并输入其他数据, 本文采取的这种中值滤波算 法仅需要7次调用3值比较器进行21次比较运算,相 对于传统的中值算法减少了近一半的计算量, 如果将 此算法利用 FPGA 做并行处理将大大提高处理速率. 算法逻辑电路如图 4 所示.

图 4 算法逻辑电路图

### 2 改进中值滤波在FPGA中实现

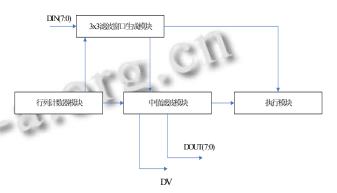

滤波器在硬件组成中主要分为三个部分:3x3 滤波 窗口生成模块, 行列计数器模块, 中值滤波模块和执 行模块[12-14]. 执行模块分别由复位信号(rstn)和时钟信 号组成(clk), 他们共同控制图像信息的输入. DIN(7:0) 为 8 位灰度图像数输入信号, DOUT(7:0)为经系统处理 后的 8 位图像出信号, DV 是输出信号有效标志. 图 5 为滤波器总体设计图.

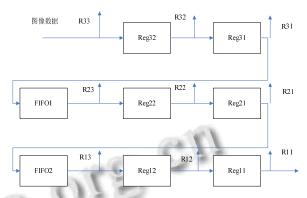

以 3x3 滤波窗口为例, 为了保证将采集到的 9 个 像素点同时输出进行运算我们采用 2 个 FIFO 存储器, 每一个 FIFO 存储器存储先被采集到的一行像素点数 据等待第三行数据采集完毕后再玉前两行的数据同时 输出构成 3x3 模板[15,16]. 为接下来的运算做好准备. 3x3 模板生成流程如图 6 所示.

滤波器总体设计图 图 5

图 6 3x3 模板生成流程

|       | 758, 000 | s     | 758, 020     | ns    | 758, 040 | ns    | 758, 060 | ns    |

|-------|----------|-------|--------------|-------|----------|-------|----------|-------|

| 189   | 19       |       | 185          | X 18  | 2        | 1     | 8        |       |

|       |          |       |              |       |          |       |          |       |

|       |          |       | $oxed{oxed}$ |       |          |       |          |       |

| 196   | 193      | 185   | 177          | 171   | 178      | 201   | 179      | 172   |

| 190   | 188      | 185   | 181          | 178   | 168      | 179   | 157      | 198   |

| 177   | 178      | 182   | 187          | 189   | 172      | 158   | 179      | 174   |

| 193   | 185      | 177   | 171          | 178   | 201      | 179   | 172      | 190   |

| 188   | 185      | 181   | 178          | 168   | 179      | 157   | 198      | 2     |

| 178   | 182      | 187   | 189          | 172   | 158      | 179   | 174      | 176   |

| 185   | 177      | 171   | 178          | 201   | 179      | 172   | 190      | 187   |

| 185   | 181      | 178   | 168          | 179   | 157      | 198   | 2        | 173   |

| 182   | 187      | 189   | 172          | 158   | 179      | 174   | 176      | 198   |

| 75789 | 75790    | 75791 | 75792        | 75793 | 75794    | 75795 | 75796    | 75797 |

| •     | -        |       | 11 66 > 1    |       |          |       |          |       |

图 7 改进算法 modelsim 仿真图

在完成滤波器硬件设计后要利用 FPGA 实现软件 对改进中值滤波的效果进行验证. 采用 verilog 语言编 写改进中值滤波代码, 并在 MATLAB 与 Modelsim 上 进行联合仿真,对比仿真结果得出结论.首先由 Matlab 读取图片数据并经过适当的处理, 然后保存为

Research and Development 研究开发 239

数据文件然后 Modelsim 中读取上述数据文件, 进行中 值滤波后将结果也写入新的数据文件. Matlab 在读取 Modelsim 中所写的数据文件, 经过适当排列处理后进 行结果验证.

图7为改进中值滤波在Modelsim上的仿真波形图, 从图中可以看出在经过了30ns左右的延迟后中值滤波 正确的实现了. 接下来利用一张噪声图片用 MATLAB 与 Modelsim 分别进行中值滤波处理, 处理效果如下 图.

加入椒盐噪声后的图像

matlab 处理图 图 9

图 10 Modelsim 处理图

为了验证本文采用的改进中值滤波比其他中值滤波 有更高的实时性及低能耗性,接下来引入多级中值滤 波将其在处理速度及 FPGA 资源利用情况方面与本文 采用方法做比较得出结论. 运算速度与资源利用比较 如下表所示.

FPGA 资源利用表

|             | Combinationa<br>functions |        | edicated<br>c registers | Memory<br>bits |  |  |  |  |

|-------------|---------------------------|--------|-------------------------|----------------|--|--|--|--|

| 传统算法        | 328                       | 11.    | 170                     | 15312          |  |  |  |  |

| 多级算法        | 203                       | 114    |                         | 12412          |  |  |  |  |

| 本文算法        | 156                       |        | 78                      | 9574           |  |  |  |  |

| 表 2 处理速度时间表 |                           |        |                         |                |  |  |  |  |

| 图序<br>算法    | 图 1                       | 图 2    | 图 3                     | 图 4            |  |  |  |  |

| 传统算法(s)     | 0.4796                    | 0.5358 | 0.5224                  | 0.6174         |  |  |  |  |

| 多级算法(s)     | 0.1237                    | 0.1475 | 0.1342                  | 0.1526         |  |  |  |  |

| 本文算法(s)     | 0.0842                    | 0.0894 | 0.8879                  | 0.9752         |  |  |  |  |

通过以上仿真比较可以看到利用 FPGA 进行的改 进中值滤波不但具有运算速度快, 实时性高、低能耗 的特点而且能够很好的去除图像中的噪声影响保证图

像边缘清晰度.

#### 结语 3

本文根据很多系统对图像处理实时性要求较高的 特性, 研究图像中值滤波的特点及基本算法, 通过改 进算法和优化结构, 在充分有效利用硬件资源的前提 下, 竟可能的发掘中值滤波算法的并行性, 利用 FPGA 集成度高、硬件并行的优势, 高效快速的进行图 像预处理设计. 通过仿真软件实现仿真结果并进行对 比, 结果显示说明本文采用的 FPGA 图像预处理系统 不但可以很好的完成中值滤波的效果而且运算速率大 大小于其他算法, 可以在一些对于实时性较高的处理 系统中有效运用. 如果在今后的研究中能够提高其在 强噪声环境中的去噪能力, 将会大大提高这种方法的 运用领域.

## 参考文献

- 1 胡学龙,许开宇.数字图像处理.北京:电子工业出版社,2007.

- 2 Chang JJ. Modified 2D median filter for impulse noise suppression in a real-time system. IEEE Trans. on Consumer Electronics, 1995, 41 (1): 73-80.

- 3 文强,侯勇严.数字图像处理.西安:西安电子科技大学出版社, 2009

- 4 尚明.FPGA 技术的应用与发展趋势.科技咨询,2007,14:10-12.

- 5 俞吉波,孔雪,郑哲,祝永新,付宇卓.FPGA 实际可用性评估与 发展趋势分析.计算机工程,2011,13:282-285.

- 6 杨海钢,孙嘉斌,王慰.FPGA 器件设计技术发展综述.电子与 信息学报.2010(03):714-723.

- 7 宁媛,李皖.图像去噪的几种方法分析比较.贵州工业大学学 报(自然科学版),2005,4(4):63-66.

- 8 张秀荣,孟和达来.数字图像处理系统的开发与研究.湖南师 范大学自然科学学报,2011,(6):35-40.

- 9景敏.数字图像处理技术的应用.机械管理开发,2011,(1):201 -203

- 10 Ng PE, Ma KK. A switching median filter with boundary discriminative noise detection for extremely corrupted images. IEEE Trans. on Image Processing, 2006, 15(6): 1506 -1516.

- 11 杨明,宋丽华.改进的快速中值滤波算法在图像去噪中的应 用.测绘工程,2011,(3):65-70.

- 12 Ci FY, Zou LJ. Dgital image processing techniques. Proc. of the IEEE International Conference on Automation and Logistics. Qing Dao. 2008. 2320-2324.

- 13 朱捷,朱小娟,贺明.基于 FPGA 的实时图像中值滤波设计. 计算机测量与控制,2007,15(6):798-800.

- 14 Chalimbaud P, Berry F. Design of an imaging system based on FPGA technology and COMS imager. Proc. of the 2004 IEEE International Conference on Field-Programmable Technology 2004: 407-411.

- 15 李雷鸣,张焕春,张波.一种基于FPGA的图像中值滤波器的 硬件设计实现.电子工程师,2004,30(2):48-50.

- 16 Zhang XX, Wang JY, Li Y. Design of high-speed image processing system based on FPGA. The 9th International Conference on Electric Measurement & Instrument ICEMI. 2009,4.65-69.