# 基于 UML 的嵌入式系统设计<sup>®</sup>

# Designs of Embedded System Based on UML

何宗奎 康积涛 (西南交通大学 电气工程学院 四川 成都 610031)

摘 要: 嵌入式系统复杂度的不断提高,对传统的系统设计方法提出了挑战。在阐述了嵌入式系统、统一建模 语言(UML)及其扩展(HRM 和 UML-RT)的概念后,探讨一种新的嵌入式系统设计流程(UHU),并结合 实际工程——基于 CPCI 的任意波形发生器予以解释。

关键词: 嵌入式系统 UML HRM UML-RT

嵌入式系统是集软、硬件于一体的专用计算机。 随着计算机技术的深入发展,实际应用所要求的嵌入 式系统的功能趋于多样化化。功能的多样化带来了设 计的复杂性,传统的嵌入式系统开发过程就显得比较 简单、笼统,越来越难以适应新的应用需求。因此, 存在对新的、能适应技术发展要求的嵌入式系统设计 方法的需求。

统一建模语言(unified modeling language, UML)是一种通用的可视化建模语言。它能用于系统开发过程的具体化、文档化。它大体上由包含系统结构和行为信息的框图组成,结构框图包括类、对象和封装,行为框图包括状态机、用例和交互图。UML是对象管理组织(object management group, OMG)所确立的标准,已为软件工程领域广泛接受[1]。近年来,伴随电子系统设计软件化和复杂化趋势。UML及其扩展逐渐被引用到嵌入式系统设计中。

硬件资源模型 (hardware resource model, HRM)是由 Safouan TAHA、Jean-Luc DEKEYSER 等人于2007年基于UML所提出的面向硬件资源的新模型<sup>[2]</sup>。它从不同视角、不同详细程度描述各硬件平台特性。它基于硬件的特性、功能、技术和外形等概念,主要由逻辑视图和物理视图组成。其主要应用包括:软件设计与配置、硬件模型的分析与仿真以及产品描述三个方面。

UML-RT(UML for Real Time),是 Rational 公司

运用 UML 扩展机制于 ROOM(Real-Time Object-Oriented Modeling language) 的 协作概念和ObjectTime 的角色建模<sup>[3]</sup>。它有助与捕获和理解系统的结构和行为模型。此外,它特别适用于建模众多实时系统的反应特性。基于 Weiguo He 和 Steve Goddard 的研究,在适当改进他们提出的 UML-RT 模型来捕获时间参数,从而进行时序分析。

#### 1 UHU建模流程

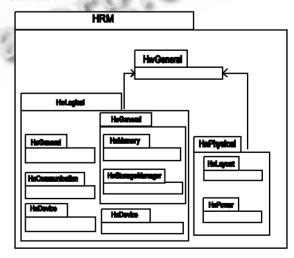

HRM 是基于嵌入式计算机的一般原理和结构的 硬件资源模型,对嵌入式硬件设计有指导性的作用。 其总体结构如图 1 所示。

图 1 HRM 模型总体结构图

① 收稿时间:2009-02-04

其中,HwGeneral 模板定义了一个硬件执行平台的典型结构。它包含了 HRM 的两个中心概念:硬件资源 HwResource 和资源服务 HwResourceService。HwRsource 表示出普通硬件实体,这些实体至少有一个 HwResourceService,来自其他资源的一些服务。另外,硬件逻辑模型 HwLogical 是为了提供硬件资源的功能性分类,这一分类主要基于每一资源所能提供的服务;硬件物理模型 Hwphysical 主要体现物理器件的实际特性,诸如器件功耗、尺寸、重量和引脚数等。

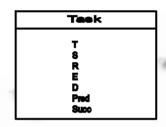

UML-RT 基于 UML 的扩展功能,利用 UML 常用的扩展方法(增加新规则或修改已有的规则)创造一个新的数据类封装。它包含有七个参数,如图 2 所示:

图 2 捕获时间参数的任务类框图

#### taskA(T,S,R,E,D,Pred,Succ),其中

T: 任务类型: 定时/周期/零星/非周期和抢占式和非抢占式:

- S: 任务开始执行的绝对时间:

- R: 任务的执行速度,如(x, y): x 在 y 时间单元执行完成:

- E: 任务可能执行的最长时间;

- D: 任务的相对响应时间;

Pred: 前一个任务,它触发当前任务动作;

Succ: 后继任务,当前任务将触发的下一任务。

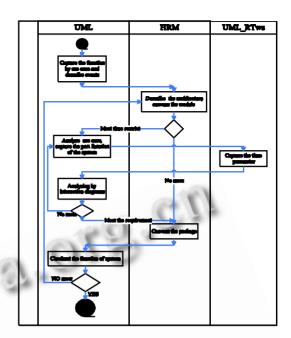

UHU 嵌入式系统设计方法的主要思想是:首先应用 UML 的用例视图捕获系统功能需求,并进行事件流的描述;然后使用 HRM 模版,对系统硬件资源进行建模;其次用 UML 的交互视图结合硬件资源模型描述用例事件流,进行设计校验;最后,若系统中的某部分电路时序要求严格,则采用 UML-RT 进行(局部)建模,然后用交互视图进行时序分析跟踪。UHU 建模流程如图 3 所示。

# 2 基于UHU的嵌入式系统设计应用

基于 CPCI 总线规范,除可以生成正弦波、方波

图 3 UHU 建模流程图

等标准波形外,可以由波形编辑软件编辑后输出任意波形。利用 DDS(直接数字频率合成)技术产生高速D/A 所需的转换时钟。使用内部参考时钟时,D/A 的转换速率从 0.04Sa/S 到 40MSa/S。DDS 的参考时钟可以从外部直接输入,频率范围 1MHz~40MHz。当使用外部参考时钟时,D/A 转化速率可在(1/232~0.23×6×fref)范围内设置,调整步长为 6×fref/232(fref 为外部参考时钟)。具有频率扫描功能,扫描的上限频率、下限频率、扫频步长及速度可设置。扫描模式包括:线性(向上或向下)和来回(向上一向下一向上或向下一向上一向下)。能进行波形延时输出、波形计数输出、输出滤波器可调、输出幅度可调、波形存储、触发同步等功能。PCB 尺寸要求:长 160,宽 100,高<20(单位: mm)。

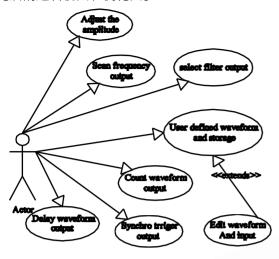

用用例图捕获系统功能,如图 4。由于篇幅所限,在此不列出事件流描述(在事件流描述中,应当详细描述每一用例的实现过程,这有利于 HRM 模型的建立和系统功能校验)。

考虑系统功能实现,系统采用可编程器件XC3S1600E来实现HwArbiter和其他功能(如DDS,通道控制等),TMS320DM642实现HwProcessor和PCI桥、控制任意波形数据的存储和处理等功能,MT48LC4M32B2实现HwRAM对数据的动态存取,图 5 中即是其例化图。类似地,可以画出其他资源细

化后的逻辑视图和例化图。

图 4 系统用例视图

# <hwRAM>> MT48LC4M32B2:SDRAM frequency=166MHz memorySize=128Mb addressSize=12bit organization=(4096;256;4;32bit) timings=('tRAS','CAS latency';2CLK) burstLengths=1,2,4,8,4K burstTypes=Sequencial,interleave refreshRate=4K/64ms refrestModes=CAS#beforeRAS#

图 5 HwStorage 逻辑视图和 HwRAM 例化

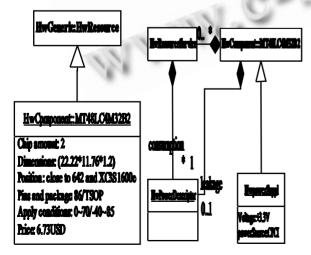

上面应用 HRM 的逻辑模型对 HwStorage 进行了建模,接下来应用硬件物理模型对 HwRAM:: MT48LC4M32B 进行建模。

图 6 HwRAM 物理模型细化

至此,我们有针对地结合项目实例中特定功能讲解了 HRM 的应用流程。接下来,针对 FPGA 访问 SDRAM 部分的时序电路,应用图 2 展示的 UML-RT 改进模型捕获时间参数,然后利用进行 UML 交互图中的顺序图进行时序建模。

| T1_precharge                                             |                                                                                           | T2_autofresh                                                                                                                                  |                                                                            | T3_loadModeRegister                                                                 |                                                                                              |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                                          |                                                                                           | T-peridok S>100m*t <sub>er</sub> *t <sub>erC</sub> R: (1,t <sub>erC</sub> ) R: d2 D: d2 Pred precharge(antalresi) Successaritesi(load modeli) |                                                                            | Taporadie<br>S>100m the +20mc<br>Res<br>Res<br>Debum<br>Predemo-fresh<br>Successive |                                                                                              |

| TO_initialing                                            | T4_active                                                                                 |                                                                                                                                               | T5_read                                                                    |                                                                                     | T6_write                                                                                     |

| T:1 8:0 R:0 E:100us D::0 Prod ouvironment Succeprocharge | T: aperk<br>S:0<br>R: (1,hc)<br>B: hco<br>D: t <sub>nco</sub> +<br>Pred: act<br>Succ: res | ).St <sub>cs</sub>                                                                                                                            | T: aperiodic S:0 R: (i,tac) E: tout tous D: <-Str. Pred: active Succ: read |                                                                                     | T: speriodic<br>S:0<br>R: (I,As;)<br>E: tous+tous<br>D: tous+tous<br>Pred: read<br>Succ: end |

图 7 用改进型 UML-RTws 捕获访问 SDRAM 时间参数

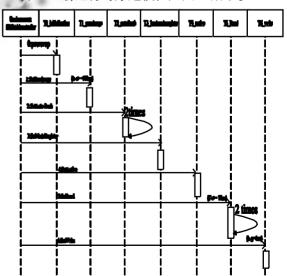

其中, tCK, tRP, tRFC, tMRD, tRC, tRCD, tCMS, tCMH 请参见芯片数据手册[4],其大小与所选的芯片以及选用芯片的功能有关。这里其时钟频率为166MHz,执行随机读,以上参数则细化为 6ns, 18ns, 6ns, 12.5ns, 60ns, 18ns, 1.5ns, 1ns。由于篇幅所限,在能充分显示 UHU 建模流程应用的前提下,只对访问 SDRAM 的一个基本过程(初始化-->预充电-->自刷新-->加载模式寄存器-->激活-->读-->读-->与)进行时序建模,如图 8 所示。

图 8 访问 SDRAM 的过程顺序图

图 8 对访问 SDRAM 的简单过程进行了充分的暴露。其中 T0~T6 为图 7 运用 UML-RTws 捕获的时间参数模型。在进行了交互视图分析后,应当按照图 3 所示的 UHU 流程,继续执行接下来的步骤——封装细化和系统功能校验,直到完成嵌入式系统设计。

## 3 结论

本文基于 UML、HRM 和 UML-RT 引出嵌入式系统设计方法 UHU,并在基于 CPCI 任意波形发生器上演示了其应用过程。UHU 充分利用了以上三种模型的优点,能够弥补传统系统设计过程的一些不足,给用户、硬件设计人员、软件编程人员和系统调试人员间的相互沟通和协作带来了方便,能够提高嵌入式系统开发的整体效率。对嵌入式系统设计有一定参考价值。

### 参考文献

- 1 王强, 贾素灵, 许珂, 等. UML 系统分析设计. 北京: 高等教育出版社, 2005.

- 2 Safou an T, Ansgar R, Sebastien G. *et al.* An Open Framework for Detailed Hardware Modeling. Industrial Embedded Systems, 2007. SIES 2007. International Symposium on 4-6 July 2007, 2007:118 125.

- 3 He WG Goddard S. Capturing an Application's Temporal Properties with UML for Real-Time, High Assurance Systems Engineering, 2000, Fifth IEEE International Symposim on. HASE Nov. 2000. 2000: 65 74.

- 4 Micron Technology Inc. MT48LC4M32B2-1MEGx 32x4 BANKS, http://www.micron.com/sdram, [2008 10 031.

C 中国科学院软件研究所 http://www.c-s-a.org.cn